惊喜与展望 2005台北秋季IDF热点回顾

分享

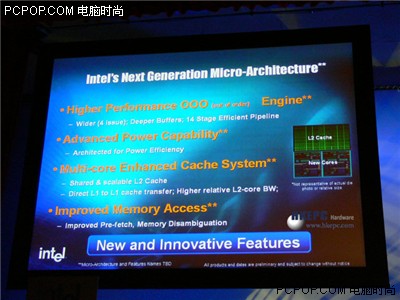

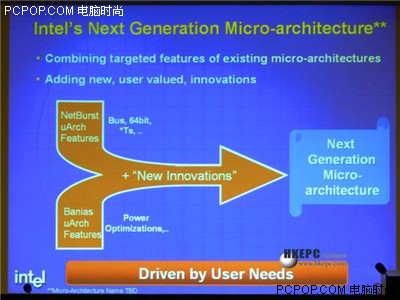

Intel在台北IDF秋季论坛提及在2006下半年度使用全新的处理器架构,声称将会把旧有Netburst架构和用在Pentium M的Banias架构结合各取所长,其中一个重大改变是由以往Pentium 4采用较长的31 Pipeline Stage,回复只有14 Pipeline Stages。以往Intel都是实行高时脉政策,而较高的Pipeline Stage无疑有助进一步提高时脉,因为Stage分得细一点的话,每个时脉所工作的份量就会较少亦能尽快完成并开始下一个指令,这样就会较易增加时脉。

可是到时脉进步至一个水平,便因为功耗、热量及制程出现瓶颈无法出现突破,而且在CPU经常使用到Branch Prediction来增加效率,但Branch Prediction并不可能100%尽确,当其中一个Stage出错的话,工作就需要重新进行,而其它需要得到这个相关这个工作的指令也很可能要重新进行,Stage越多预支结果出错时所做成的牵连及延误,因此较长的Pipeline Stage虽则可以令时脉易于提高,但在不少情况下效率会比时脉较慢但拥有较少Pipeline Stage的处理器还要差。结果下代处理器将会采用Pentium M较少的Pipeline Stage架构,虽然时脉较低但效率却比现时采用NetBurst的Pentium 4要好,最重要功耗有明显的改善,Intel处理器不再是发热机器了。

0人已赞

第1页:Intel推广WiMAX 台湾将启动最新无线网络第2页:完全超越传统CCFL 东芝松下最新LED技术第3页:2006年Q1出货 全球首颗双核Pentium M敲定第4页:省电30%以上 双核Pentium M的强化休眠模式第5页:代号“Whitefield” Intel四核心处理器首曝第6页:流水线将减少 Intel处理器的未来发展动向第7页:支持FB-DIMM内存 北桥带宽将提升至17GB/s第8页:主频达到1248MHz 第四代XScale处理器亮相第9页:代号“NVM Cache” 新一代NB系统加速技术第10页:峰值功耗79.3W 现场展示Sossaman Xeon平台

关注我们