最新赛扬D绝配!ATI RXC410对决915PL

DDR2是今年仅次于PCIE转型风暴的第二大技术革命,此次有着Intel联合众DRAM模组厂商的支持让DDR2内存的底价在短短半年内被数次刷新,目前它的售价甚至比DDR SDRAM还低,已经具备了挑战DDR SDRAM的时机和条件。

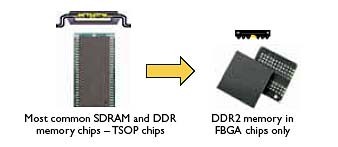

DDR2内存拥有4bit的数据预读取能力,虽然与DDR一样,都采用了在时钟的上升延和下降延同时进行数据传输的基本方式,但是在同等核心频率下,DDR2拥有两倍于DDR的数据传输率。DDR2内存采用FBGA封装,提供了比TSOP封装更好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的提升提供了良好的保障。DDR2内存采用1.8V电压,相对于DDR标准的2.5V,降低了不少,从而提供了更小的功耗与更小的发热量。

现在的DRAM内部都采用4个bank的结构,每个bank由存储单元队列构成,存储单元队列通过行和列地址定位。从内存的读操作中可以了解到内存工作的几个瓶颈,它们分别是内存单元的再存储和预充电的延时,这个延迟属于bank内部的延迟,由于DRAM结构的限制这个延迟本身不太好解决。还有内部数据总线的频率限制,内部数据总线是连接DRAM颗粒中4个bank的总线,最后一个DRAM的瓶颈是输入/输出电路的延迟。

DDR SDRAM | DDR2 SDRAM | |

频率 | 200/266/333/400 MHz | 400/533 (667/800)MHz |

封装 | TSOP and FBGA | FBGA |

电压 | 2.5V | 1.8V |

容量 | 64 Mbit -1Gbit | 256 Mbit -4Gbit |

Internal Banks | 4 | 4 and 8 |

Preftch (MIN Write Burst) | 2 | 2 |

Cas Latency (CL) | 2,2.5,3 | 3,4,5 |

Additive Latency ( | NO Support | 0,1,2,3,4 |

Read Latency | CL | CL+AL |

Write Latency | 1 | Read Latency -1 |

On-Chip Bus Termination | None | Embedded |

Burst Lengths | 2,4,8 | 4,8 |

从上表可以看出,在同等核心频率下,DDR2的实际工作频率是DDR的两倍。这得益于DDR2内存拥有两倍于标准DDR内存的4BIT预读取能力。换句话说,虽然DDR2和DDR一样,都采用了在时钟的上升延和下降延同时进行数据传输的基本方式,但DDR2拥有两倍于DDR的预读取系统命令数据的能力。也就是说,在同样100MHz的工作频率下,DDR的实际频率为200MHz,而DDR2则可以达到400MHz。然而,这个方法虽然可以有效果提高内存带宽,但也有它最主要的缺点就是高延迟。内存延迟不取决于I/O缓冲区的工作频率或数据从存储单元进入总线的位宽多少。影响延迟的主要因素是内存存储单元自身的延迟。也就是说,在同样100MHz的工作频率下,DDR的实际频率为200MHz,而DDR2则可以达到400MHz。

因此,早期的DDR2同DDR相比起来并没有占到多少便宜,反而是DDR2内存受高延迟的影响,性能要略逊色于同频的DDR内存平台。因此目前支持DDR2 SDRAM的内存厂商一些努力解决这个问题,现在他们取得了一定的成绩。在基于i915/925芯片组的平台上,早期DDR2-533 SDRAM模块仅能工作在4-4-4 timings模式下。不过目前这种情况已经有所改观,许多内存制造商,特别象Corsair或OCZ此类为PC发烧友推出先进内存模块的内商,已经推出了支持3-3-3 timings规格、工作频率为533MHz的DDR2 SDRAM内存模块。而这些内存模块并非通过超频获得的,而是完全符合JEDEC标准。

关注我们