全新酷睿2架构!Merom vs. Yonah对比

Intel新一代Core微架构移动处理器Merom正式登场,将移动计算机性能推升至新纪元,究竟Merom和Yonah在微架构上有何不同、Centrino平台Napa Refresh与即将在2007年Q2面市的Santa Rosa之间差异何在!?HKEPC编辑部找来Intel Core 2 Duo T7600与上代Core Duo T2700,作性能对比测试。

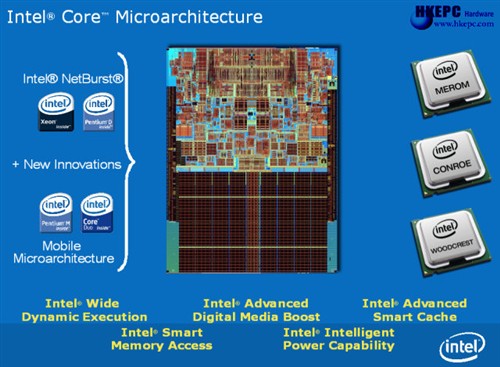

● 全新Core微架构-- Intel Merom移动处理器

尽管Intel Core微架构是基于Mobile平台的Yonah核心所设计,但却有超过7成的架构和线路被重新改良,并加入5项主要的改革,包括Intel Wide Dynmaic Execution、Intel Intelligent Power Capability、Intel Advanced Smart Cache、Intel Smart Memory Access及Intel Advanced Digital Media Boost。

Core | Mobile Dual Core | NetBurst | AMD | |

L2 Cache | Shared L2 & Higher BW | Shared L2 | Independent L2 | Independent L2 |

L2 Cache Size | 4MB | 2MB | 2MB x 2 | 512KB x 2 |

SSE Throughput | 128Bit/Cycle | 64Bits/Cycle | 64Bits/Cycle | 64Bit/Cycle |

Issue Width | 4 Issue | 3 Issue | 3 Issue | 3 Issue |

Pipeline Stage | 14 Stage | 13 Stage | 31 Stage | 12 Stage |

System Bus | Up to 800MHz for | Up to 667MHz | Up to 1066MHz | 800MHz HT |

Power Efficiency | Ultra Fine Power Gating | Aggressive Power Gating | Power Gating | Power Gating |

Memory Access | Improved Prefetch | Baseline Prefetch | Baserline Prefetch | Integrated Memory Controller |

Intel Wide Dynamic Execution -- Merom处理器拥有4组Decoder (3 Simple decoders + 1 Complex Decoders),比上代Yonah核心多出1组(2 Simple Decoders + 1 Complex Decoders) 可多处理1组Simple Coder指令, 进一步提升每周期的执行效率及提升处理器的能源效益。

虽然Merom的Pipeline Stage由Yonah的13 Stage轻微上升至14 Stage,但Merom的Branch Predictor Bandwitdh提升20Bytes(Yonah为16Bytes), 因此其分支预测的能力及准确性效率保持相若。

此外,Merom处理器不单保留了Micro-op Fusion技术,并同时追加全新的 Macro-Fusion 技术,在旧世代的微架构中,每个指令被送来时其译码及执移动作是完全独立的,但Intel Core微架构可以让常见的指令组,例如1个Compare指令配随后拥有1个Jump指令,组合成单一的Micro-Op指令,这令Merom处理器在特定情况下每个周期有运算5组指令,据Intel表示,大部份x86程序,约每10至15个指令就会出现1组可透过Macro -Fusion被组合,因此减少了程序执行所需运算时间、提升性能却不会增加处理器的功耗,为此Intel亦改良ALU(Arithmetic Logic Unit)部份以支持Macro-Fusion技术。

Intel Intelligent Power Capability -- Merom处理器的晶体管数目对比Yonah大幅提升,功耗消耗亦会相对增加,而为令Merom处理器的功耗表现保持于合理水平,Merom加入Ultra Fine Grained省电设计,细微的逻辑控制机能独立开关各运算单元,只有需要时才会被开启,避免闲置时出现不必要的功耗浪费,称为 Sleep Transistors技术,此外,把核心各个Buses及Array采用独立控制其VCC电压,当此部份被闲置时,将会被运作于低功耗模式中,因此Merom处理器在功耗表现可保持和Yonah处理器相约。

Intel Adcanced Smart Cache -- 早在Yonah处理器中,Intel已加入了Smart Cache架构,通过核心内部的Shared Bus Router共享相同的L2 Cache,而Merom进一步加强Prefetch能力,每颗核心均拥有3个独立Prefetchers (2 Data and & 1 Instruction) 及2个L2 Prefetchers,能同时地侦出Multiple Streaming及Strided Acess Patterns,L2 Cache方面比Yonah倍增至 16-Way 256Bit 4MB容量,但Latechy却保持在12-14ns之间,令Merom处理的Cache架构性能进一步提升。

Intel Smart Memory Access -- 为了提升内存读取效率, Merom处理器加入全新的内存读取技术称为Memory Disambiguation,透过Out of Order过程把内存读取次序作出分析,当发现某数据是完全独立,则可让它提早执行以减少处理器的等候时间减少闲置,同时减低内存读取的延迟值。

Intel Adavanced Digital Media Boost -- Merom处理器拥有128Bit-SIMD interger arithmetic及128bit SIMD双倍精准度Floating-Point Operations。传统的处理器设计只有64Bit的SIMD interger arithmetic及Floating-Point Operations,因此在执行 128Bit的SSE、SSE2及SSE3指令时,需要把指令分拆为2个64Bit指令,并需要2个频率周期完成,但Core微架构则只需要1个频率调期便能完成,执成效率提升达1倍,现时SSE指令集已经十分普遍地用于主流的软件中,包括绘图、影像、音像、加密及数学运算等用途,单周期128Bit处理器能力以频率以外的方法提升性能,令处理器拥有高能源效益表现。

关注我们