重拾三级缓存 AMD四核"巴塞罗纳"解析

Intel将在下月正式发布四核处理器,而AMD至少还要等上半年,但这并不意味着在四核处理器的对决中,AMD就100%会输,因为其新一代K8L相当值得期待。今天我们就带您详细了解一下AMD K8L架构首款核心Barcelona(巴塞罗纳)的情况。

巴塞罗纳是西班牙东北部的美丽港市,用其作为新一代处理器的代号,也显示了AMD的良苦用心。一般来讲,处理器架构从概念到实物出货,需要经过很长的周期,所以说在K8L架构上,AMD肯定已经下了大工夫。虽然目前来看Intel Core微架构独领风骚,但到明年中期四核市场成熟时鹿死谁手,还未可知。

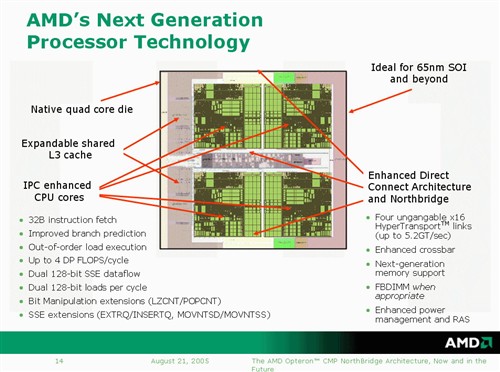

AMD Barcelona四核架构图

AMD Barcelona四核架构图

Barcelona核心可以说是由目前AMD x86-64架构上改进而来,他和当前Opteron的关系,就好比Core 2与Pentium M一样。今天我们文章中涉及到的Barcelona细节内容,出自该核心性能模型小组主导人Ben Sander之口,所以真实性很高很高。

● 提升浮点运算性能

Barcelona不仅是下代工作站/服务器处理器Opteron的核心,同时也将是AMD下一代桌面产品的基础,虽然两者之间会有些许不同,但设计方向应该是一致的。所以这一新四核必须满足以下两方面的需求。

- 具有超高的科学计算性能,具体包括财务分析、石油勘探和生物学计算等。

- 多媒体编/解码能力:HD-DVD播放和视频压缩等

这两方面的应用交集,可以说是对处理器浮点运算能力的要求。在过去的10年中,软件已经渐渐向SIMD浮点运算发展,所以相对于过去的Opteron处理器,AMD这次大幅强化了Barcelona的SSE单元,下面的表格给出了具体的细节:

新特性 | 当前架构 | |

SSE execution width | 64 bits wide | 128 bits wide |

Instruction fetch bandwidth | 16 bytes/cycle | 32 bytes/cycle |

Data cache bandwidth | 2 x 64 bit loads/cycle | 2 x 128 bits loads/cycle |

L2 cache/memory controller bandwidth | 64 bits/cycle | 128 bits/cycle |

Floating-point scheduler depth | 36 dedicated x 64-bit ops | 36 dedicated x 128-bit ops |

此外SSE MOV指令将可以在浮点"store"管线中执行,两个SSE操作可以分别在两个周期以SSE move方式执行。同时,Barcelona还支持非联盟加载/执行(load/execute)模式,这样可以使指令的封装和解码更加高效。

以上这些变化与Intel Core微架构已经采用的方式有些类似,不知道届时SSE高负载应用下,Intel和AMD谁的处理器表现更好呢。

关注我们