重拾三级缓存 AMD四核"巴塞罗纳"解析

分享

● Barcelona核心IPC进一步增强

自从Core微架构发布后,人们越来越开始强调IPC(instructions per cycle,每周期执行的指令数)的重要性,当然AMD在Barcelona上也对这一方面进行了加强。和Intel不同的是,AMD并没有采用增宽指令管线的方式来实现,而是用了其他一些方法。

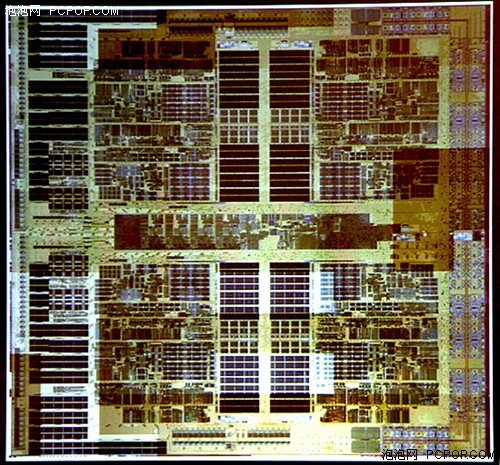

Barcelona核心照片曝光

Barcelona核心照片曝光这些增强包括:

- Advanced branch prediction(增强分支预测),AMD的工程师们使Barcelona的返回堆栈容量加倍,并且加入了更多的分之历史位,内置了512-entry间接分支预报器。

- 32-byte instruction fetch(32字节指令存取),提高指令存取的效率。

- Sideband stack optimizer(频带堆栈优化),对堆栈的处理器进行优化,使其不浪费执行单元的位宽。

- Out-of-order load execution(乱序载入执行),加强乱序执行能力,使L2缓存的延迟达到最小化。

此外,其他方面的改进还包括优化TLBs (translation lookaside buffers),额外的快路径指令和扩展位操作和SSE指令等。

● Barcelona中的内存带宽改进

AMD通过以下几个方面来提升Barcelona的内存带宽性能:

处理器核心将拥有完全独立的内存控制器,这样可以提供更多的内存页来保持打开状态,此外,内存控制器将支持48位硬件级寻址,理论上可以支持256TB的物理内存!除了常规的4KB和2MB页尺寸外,AMD这次还拿出了1GB容量的内存页。

● 重拾三级缓存架构

Barcelona将采用三级缓存架构,其中L1缓存容量为64KB,L2缓存容量512KB,L3容量为2MB。L1和L2缓存和以前一样,为各自的核心独立配备,而L3缓存则是所有核心共享使用。在设计上,L3缓存的容量是一个可以变化的数值,不同的产品将提供不同容量的L3缓存。

AMD表示采用这样的三级缓存设计架构,不仅可以在性能上得到提升,同时也将更有利于配合虚拟化技术的使用。

新一代处理器上,AMD也对硬件级虚拟化进行了加强,其中最重要的一点变化是虚拟化寻址转移代替了之前的影像分页,这将进一步降低虚拟管理程序操作影像页的时间。

0人已赞

关注我们