重拾三级缓存 AMD四核"巴塞罗纳"解析

Intel将在下月正式发布四核处理器,而AMD至少还要等上半年,但这并不意味着在四核处理器的对决中,AMD就100%会输,因为其新一代K8L相当值得期待。今天我们就带您详细了解一下AMD K8L架构首款核心Barcelona(巴塞罗纳)的情况。

巴塞罗纳是西班牙东北部的美丽港市,用其作为新一代处理器的代号,也显示了AMD的良苦用心。一般来讲,处理器架构从概念到实物出货,需要经过很长的周期,所以说在K8L架构上,AMD肯定已经下了大工夫。虽然目前来看Intel Core微架构独领风骚,但到明年中期四核市场成熟时鹿死谁手,还未可知。

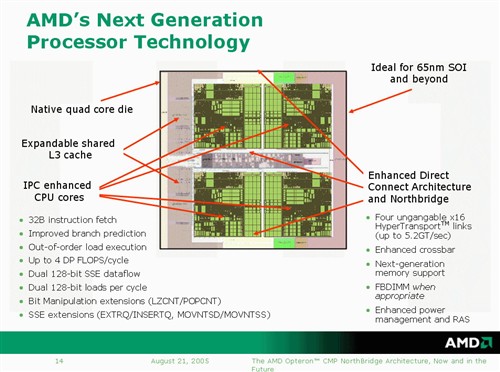

AMD Barcelona四核架构图

AMD Barcelona四核架构图

Barcelona核心可以说是由目前AMD x86-64架构上改进而来,他和当前Opteron的关系,就好比Core 2与Pentium M一样。今天我们文章中涉及到的Barcelona细节内容,出自该核心性能模型小组主导人Ben Sander之口,所以真实性很高很高。

● 提升浮点运算性能

Barcelona不仅是下代工作站/服务器处理器Opteron的核心,同时也将是AMD下一代桌面产品的基础,虽然两者之间会有些许不同,但设计方向应该是一致的。所以这一新四核必须满足以下两方面的需求。

- 具有超高的科学计算性能,具体包括财务分析、石油勘探和生物学计算等。

- 多媒体编/解码能力:HD-DVD播放和视频压缩等

这两方面的应用交集,可以说是对处理器浮点运算能力的要求。在过去的10年中,软件已经渐渐向SIMD浮点运算发展,所以相对于过去的Opteron处理器,AMD这次大幅强化了Barcelona的SSE单元,下面的表格给出了具体的细节:

新特性 | 当前架构 | |

SSE execution width | 64 bits wide | 128 bits wide |

Instruction fetch bandwidth | 16 bytes/cycle | 32 bytes/cycle |

Data cache bandwidth | 2 x 64 bit loads/cycle | 2 x 128 bits loads/cycle |

L2 cache/memory controller bandwidth | 64 bits/cycle | 128 bits/cycle |

Floating-point scheduler depth | 36 dedicated x 64-bit ops | 36 dedicated x 128-bit ops |

此外SSE MOV指令将可以在浮点"store"管线中执行,两个SSE操作可以分别在两个周期以SSE move方式执行。同时,Barcelona还支持非联盟加载/执行(load/execute)模式,这样可以使指令的封装和解码更加高效。

以上这些变化与Intel Core微架构已经采用的方式有些类似,不知道届时SSE高负载应用下,Intel和AMD谁的处理器表现更好呢。

● Barcelona核心IPC进一步增强

自从Core微架构发布后,人们越来越开始强调IPC(instructions per cycle,每周期执行的指令数)的重要性,当然AMD在Barcelona上也对这一方面进行了加强。和Intel不同的是,AMD并没有采用增宽指令管线的方式来实现,而是用了其他一些方法。

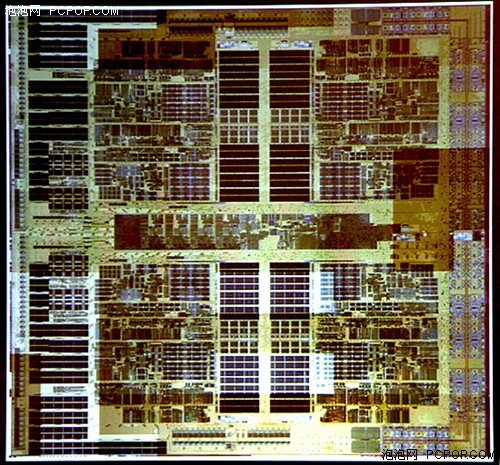

Barcelona核心照片曝光

Barcelona核心照片曝光这些增强包括:

- Advanced branch prediction(增强分支预测),AMD的工程师们使Barcelona的返回堆栈容量加倍,并且加入了更多的分之历史位,内置了512-entry间接分支预报器。

- 32-byte instruction fetch(32字节指令存取),提高指令存取的效率。

- Sideband stack optimizer(频带堆栈优化),对堆栈的处理器进行优化,使其不浪费执行单元的位宽。

- Out-of-order load execution(乱序载入执行),加强乱序执行能力,使L2缓存的延迟达到最小化。

此外,其他方面的改进还包括优化TLBs (translation lookaside buffers),额外的快路径指令和扩展位操作和SSE指令等。

● Barcelona中的内存带宽改进

AMD通过以下几个方面来提升Barcelona的内存带宽性能:

处理器核心将拥有完全独立的内存控制器,这样可以提供更多的内存页来保持打开状态,此外,内存控制器将支持48位硬件级寻址,理论上可以支持256TB的物理内存!除了常规的4KB和2MB页尺寸外,AMD这次还拿出了1GB容量的内存页。

● 重拾三级缓存架构

Barcelona将采用三级缓存架构,其中L1缓存容量为64KB,L2缓存容量512KB,L3容量为2MB。L1和L2缓存和以前一样,为各自的核心独立配备,而L3缓存则是所有核心共享使用。在设计上,L3缓存的容量是一个可以变化的数值,不同的产品将提供不同容量的L3缓存。

AMD表示采用这样的三级缓存设计架构,不仅可以在性能上得到提升,同时也将更有利于配合虚拟化技术的使用。

新一代处理器上,AMD也对硬件级虚拟化进行了加强,其中最重要的一点变化是虚拟化寻址转移代替了之前的影像分页,这将进一步降低虚拟管理程序操作影像页的时间。

● 电源管理 核心与内存控制器分离

人们已经开始越来越在乎处理器的功耗水平,在过去的很长时间里,AMD一直在这方面处于领先地位,但是自Intel发布酷睿2后,这种优势已经不复存在,AMD希望通过Barcelona重新夺回失去的光芒。主要的改进手段如下:

首先,Barcelona将基于AMD 65nm SOI工艺技术,这将让处理器的电压更低,在提升电路密度的同时,热量输出不会提高。处理器本身将和内存控制器单独供电,这样在内存控制器处于满载状态时,处理器也不会跟着满载,提高电源的利用率。

其次,Barcelona还将支持新版本的AMD PowerNow技术,先前PowerNow可以自动根据情况降低处理器频率,而进入多核时代,新版PowerNow可以对每个核心的频率进行控制,当只需要一个核心负载的时候,其他三个核心可以运行在很低的频率上。提醒一句,PowerNow并不会控制每个核心的电压。

AMD表示Barcelona的TDP不会超过95W,一个双处理器系统,加上内存、芯 片组功耗应该不会超过240W这个水平。

● 厚积薄发 AMD首发“真”四核

总体来看,Barcelona并不会像Intel Core微架构相比NetBurst那样有巨大的改变,但是新一代四核在性能上必然将有不小的提升,但具体的提升幅度,目前还无从考证。AMD方面目前也没有公布过任何有关性能的说明。

AMD有望在年底前展示基于Barcelona四核处理器的系统,实际的处理器出货要等到2007年中期,在这之前,我们还无法了解其性能的高低。可以肯定的是,Barcelona肯定会比今天的Opteron更快,但与Intel对比是否有竞争力,还是个问号。

Intel下月将抢先发布四核处理器

Intel下月将抢先发布四核处理器

AMD桌面四核也将在明年下半年发布,这样来看,在未来的6-7个月里,Intel在四核发布将保持领先地位。不过AMD已经表示,Intel即将发布的Kentsfield四核,实际是将两颗双核封装在一起而成,并不是真“四核”,但不知道消费者是否会在意这个问题。<

关注我们