45纳米微架构 Penryn处理器效能实测

此外,Penryn处理器家族的L2 Cache容量将会有所上升,双核心将拥有最可6MB、四核心更拥有达12MB容量,而且Penryn并不是单纯提升容量以增加命中率,同时亦把L2 Cache Associativity由上代的16 Way提升至24 Way,令L2 Cache存取的Latency有望进一步下降。

Penryn处理器家族将会首次加入47条Intel SSE4指令集,包括了14条向量绘图运算及3D游戏加速指令、32条视像编码加速指令及2条协同处理加速指令。

据Stephen Fischer指出,14条向向量绘图及3D游戏运算指令,让4x4 SAD、Subpixel Filtering及Search动作运算速度提升1倍。32条视像编码指令,只要软件支持SSE4指令集,编码所需时间将减少一半。而2条协同处理加速指令,令协同处理器如GPU、PPU等,在Streaming Load方面比以往速度提升9倍。

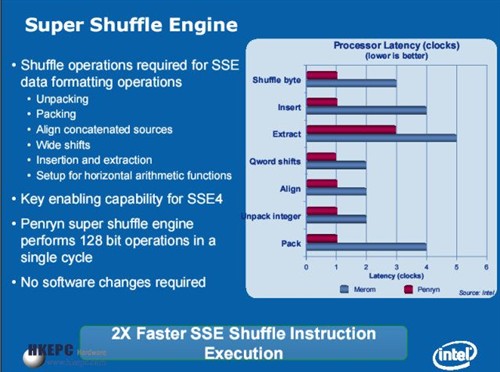

Stephen Fischer进一步指出,Penryn处理器不单加入多SSE4指令集,同时亦加入全新Super Shuffle Engine,令SSE指令运算运算更具效率,以往要处理Unpacking、Packing、Align Concatenated Sources、WideShifts、Insertion及Horizontal Arithmertic Functions Setup等指令时,均不可能在单一个周期内完成,但Super Shuffle Engine设计则让这些不同种类的128Bit SSE指令,在一个周期内便可完成,令SSE指令执行效率平均提升一倍,而且更不用在软件端中作出改良便可实现。

根据Intel最新处理器规划,DT、NB及入门级服务器平台将会于2007年下半年导入45纳米Penryn家族,而多路服务器的Penryn处理器要在2008年中才上阵。核心频率将会在3GHz以上,首款型号为3.33GHz,TDP方面则保持上代相同水平,前端汇排流方面,DT与NT将会保持1333MHz FSB及800MHz、服务器则提升至1600MHz FSB。

此外,Intel亦会保持每一年更新现有微架构、每两年更换全新微架构,预计2008年下半将会推全新45纳米NEHALEM微架构,2009年下半年则拥有32纳米更新版本,并改良了NEHALEM微架构的WESTMERE,2010年下半年全新微架构SANDY BRIDGE将紧接上场。

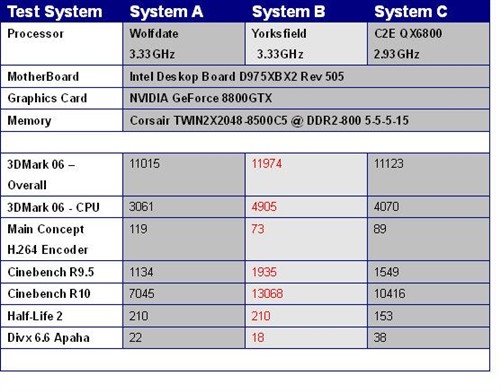

于北京IDF大会期间,部份主要媒体获安排实测Penryn处理器4核心Yorksfield (3.33GHz/6MB L2 x 2/1333MHz FSB)、双核心Wolfdale(3.33GHz/6MB L2/1333MHz FSB),对于现时最强的Intel Core 2 Extreme X6800(2.93GHz/4MB x 2 L2/1333MHz FSB),其中DivX因主援SSE4指令,拥有一倍效能增益、Half-Life 2则因大量采用平方根运算,亦拥有近四成的增益,效果令人满意。<

关注我们