多核革命 AMD首席技术官帮你解密CPU

◎ 加入异构处理器核心

显而易见,假设不同的资源的成本不同,同类多核芯片不能面向不同工作负载进行优化。若将设计空间扩大加入异构处理器核心,则可增加很多新的自由度。内核间可能不同的参数包括:基本ISA、ISA扩展、缓存容量、频率、Issue宽度、乱序功能。

这一额外的自由度令同质化的多核设计产生了无数的新可能性,既令人兴奋又令人畏惧。

当然,多核心处理器将不限于仅包含CPU。既然三维图形处理卡已经广泛整合到移动、客户端和工作站系统中,那么将图形处理单元(或图形处理单元的一部分)集成到处理器芯片上应该是自然而然的(详情请参阅AMD已发布的“Fusion”计划)。其他类型的异构架构也将成为未来合乎逻辑的选择,但目前来看,好像还没有哪个AMD的竞争对手进行过具有大规模处理器生产意义上的异构化尝试。

◎ CPU未来会有多少个核心?

虽然片内集成4到8个CPU核心的短期展望着实令人兴奋,但是,从更长期的角度来看,片内集成32、64、128、256个核心也将带来其他挑战。

1990年代末,在RISCSMP市场的鼎盛时期,大型(8路到64路)系统成本昂贵,且几乎始终共享使用。单个用户基本不用担心找不到足够多的工作使CPU保持忙碌。与之相反,即将推出的多核心处理器芯片将是价格适中的商业化产品。个人将能够轻松地负担多个CPU,超过以往“任务并行化”所需要的CPU数量。例如,在2004年,一台基于AMD或英特尔单核心处理器的高配置双插槽服务器售价为5,000到6,000美元,拥有5万美元预算的科研人员/工程师,可以购买大约8台服务器(16个内核)以及足够的存储与网络设备。自2000年开始,这类系统的数量剧增,很多用户发现在小型集群上,运行独立串行作业时,或仅在一个服务器内进行并行作业(使用OpenMP或明确的线程)时,可以充分使用这些小集群的资源。

若厂商提供近乎同样的价格,则使用相同的预算,采用16核的处理器将总共获得256个核心。科研人员/工程师用户基本不会有数量如此巨大的独立作业(通常,通过参数检查、敏感度分析或整体统计产生),也不会考虑改进此吞吐量,以提高单一作业性能。

更进一步的设想,若使用5万美元能采购128核的芯片,将获得2048个线程,这将使绝大多数用户编程和使用计算机的方式发生根本性变革。因此,多核心处理器开发人员的任务很艰巨,他们必须简化多核心处理器的开发,以提高单一作业的效率。并且,如果多核用户能够提前于自己的竞争对手,率先开发出此并行机制,则该用户将获得更多的竞争优势。

关注我们

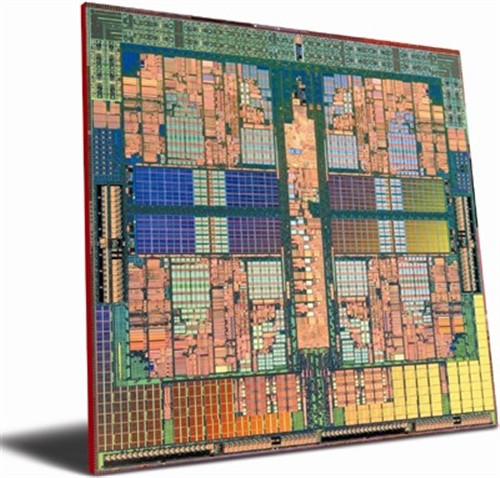

AMD K10 Phenom X4核心照

AMD K10 Phenom X4核心照