Phenom VS Penryn 双雄大战锁定年底

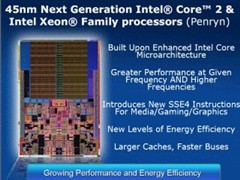

● Intel 45nm处理器大军Penryn铁定本年第四季上阵

2006年下半年,Intel正式发布新一代「Core」微架构,取代面市5年、疲态毕露的「Netburst」微架构,成功令Intel谷底回春,重新站上x86处理器产品领导地位,而为保持此一优势,Intel同时也宣布全新「规则律动」「Tick-Tock」硅与微架构发展战略,于每年推出新处理器技术时,皆具备改良的微架构或是全新设计微架构,以迎合未来十年甚至更远的处理器市场。

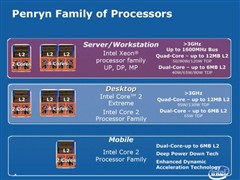

全新45nmPenryn家族共有7名成员,包括双核心桌面处理器Wolfdate、四核心桌面处理器Yorkfield、双核心行动处理器 Penryn、双核心Xeon DP处理器 Wolfdate DP、四核心 Xeon DP处理器Harpertown、双核心 Xeon MP处理器Dunnington DC及四核心Xeon MP处理器Dunnington QC。

Penryn双核心版本内建 4.1 亿个晶体管,四核心则有8.2亿个晶体管,微架构经强化后,在相同频率下较上代Core产品拥有更高性能,同时L 2 Cache容量亦提升50%,明显提高数据读取执行的命中率。此外,亦加入47条全新Intel SSE4指令,提高媒体性能和实现高性能运算应用。

● 全新45nm High-K金属栅极技术 能效表现再提高

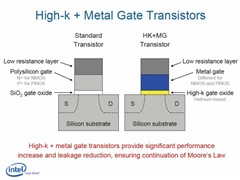

由于深知漏电问题将会阻碍芯片和个人计算机的设计、大小、耗电量、噪声与成本开发,因此,新一代Penryn处理器家族将采用全新材料制作的45nm晶体管绝缘层(insulating wall)和开关闸极 (switching gate),减低晶体管漏电(electrical leakage)情况。

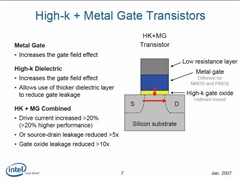

为能达到大幅降低漏电情形且可同时提升效能目标,Intel采用被称为High-k的新材料制作晶体管闸极电介质(transistor gate dielectric),而晶体管闸极的电极 (transistor gate electrode)也将搭配采用全新金属材料组合,增加驱动电流20%以上,不仅提升晶体管效能,同时源极 - 汲极 (source-drain) 漏电也可减少逾5倍,明显改善晶体管耗电量。

据了解,由于二氧化硅具有易制性 (manufacturability),且能减少厚度以持续改善晶体管效能,因此过去40余年来,业者主要均采用二氧化硅做为制作闸极电介质的材料。

虽然Intel于导入65nm制程时,已全力将二氧化硅闸极电介质厚度降低至1.2nm,相当于5层原子,但由于晶体管缩至原子大小的尺寸时,耗电和散热亦会同时增加,产生电流浪费和不必要的热能,因此若继续采用目前材料,进一步减少厚度,闸极电介质的漏电情况势将会明显攀升,令缩小晶体管技术遭遇极限。

为解决此关键问题,Intel正规划改用较厚的High-k材料(铪hafnium元素为基础的物质)作为闸极电介质,取代沿用至今已超过40年的二氧化硅,此举也成功令漏电量降低10倍以上。

由于High-k闸极电介质和现有硅闸极并不兼容,Intel全新45nm晶体管设计也必须开发新金属闸极材料,目前新金属的细节仍属商业机密,Intel现阶段尚未说明其金属材料的组合。

另与上一代技术相较,Intel的45奈制程令晶体管密度提升近2倍,得以增加处理器的晶体管总数或缩小处理器体积,令产品较对手更具竞争力,此外,晶体管开关动作所需电力更低,耗电量减少近30%,内部连接线 (interconnects) 采用铜线搭配 low-k电介质,顺利提升效能并降低耗电量,开关动作速度约加快 20%。

值得注意的是,Intel成功令新一代 45 nm制程产品的漏电情况降低逾5倍,其中晶体管闸极氧化物漏电量更降低超过10倍,相较上代65nm制程产品,在同一功耗表现下,频率下可提升约20%,或是在同一频率下功耗更低,电池续航力也明显大幅提升。

另一方面,Intel使用创新设计法则和先进光罩技术,将193nm干式微影技术 (dry lithography) 延伸应用在45nm处理器上,全力发挥成本优势和高易制性。

关注我们