Intel十年回顾 五大架构鉴证CPU历程

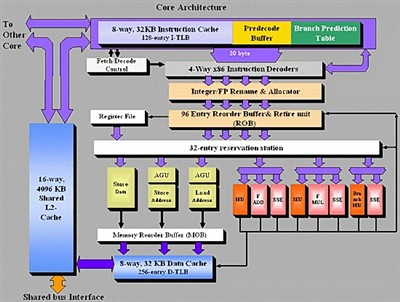

Core微架构要优于Pentium 4和Athlon 64所采用的技术,其中的每个核心至少有3组预取单元,包括2组数据预取单元和1组指令预取单元。除此之外,共享式二级缓存还拥有2组预取单元。这样,在一个双核心的采用Core微架构的处理器中,共有8组预取单元。有一个问题是,多达8组的预取单元在进行预取工作时,很容易会妨碍到正在运行的程序的正常的load操作。为了避免这种情况的发生,Core微架构采取了预取监测器的机制,该监测器总会给予正在运行的程序更高的优先级。这样,预取单元就决不会从正在运行的程序那里“偷”走很多带宽了。

Core微架构的预取机制还有更多新特性。数据预取单元经常需要在缓存中进行标签查找。为了避免引起正在运行的程序进行的标签查找的更高的延迟,数据预取单元使用标签查找的store端口。如果你还记得,load 操作的发生频率是store操作的2倍之多,那么就容易理解这样的选择了——store 端口的使用频率仅为 load 端口的一半。并且,store操作在大多数情况下并不是影响系统性能的关键,因为在数据开始写入后,处理器可以马上开始进行下面的工作,而不必等待写入操作完成。缓存/内存子系统会负责数据的整个写入到缓存、复制到主内存的过程。

Core微架构的缓存系统也令人印象深刻。二级缓存容量高达4MB,并且是由两个核心共享的,访问延迟仅12到14个时钟周期。每个核心还拥有32KB的一级指令缓存和一级数据缓存,访问延迟仅仅3个时钟周期。从 NetBurst 微架构开始引入的追踪式缓存(Trace Cache)在Core微架构中消失了。NetBurst 微架构中的追踪式缓存的作用与常见的指令缓存相类似,是用来存放解码前的指令的,对 NetBurst 微架构的长流水线结构非常有用。而Core微架构回归相对较短的流水线之后,追踪式缓存也随之消失,因为Intel认为,传统的一级指令缓存对短流水线的Core微架构更加有用。

现在处理器的发展已经不是只强调计算速度,而是多方面的追求,如功耗、发热量等多方面的发展。可以说新一代Core构架的处理器是Intel朝高性能、低功耗、低发热量等方面的一个新的起点。相信,Intel处理器随着构架的不断更新,工艺的不断提高,其产品能改变人们的生活,满足消费者的需求。<

关注我们