三通道+DDR3能普及吗?内存变革进行时

● DDR3集万千宠爱抢班夺权

1. 8bit预取设计,而DDR2为4bit预取。

相对于DDR2内存的4bit预取机制,DDR3内存模组最大的改进就是采用了8bit预取机制设计,也就是内部同时并发8位数据。在相同Cell频率下,DDR3的数据传输率是DDR2的两倍。这样DRAM内核的频率只有接口频率的1/8,DDR3-800的核心工作频率只有100MHz,当DRAM内核工作频率为200MHz时,接口频率已经达到了1600MHz。而当DDR3内存技术成熟时,相信有实力的内存厂商将推出DDR3-2000甚至2400的频率更高的内存。

内存规格对比表

内存规格对比表

2. 采用点对点的拓朴架构,以减轻地址/命令与控制总线的负担。

这是为了提高系统性能而进行的重要改动,也是DDR3与DDR2的一个关键区别。在DDR3系统中,一个内存控制器只与一个内存通道打交道,而且这个内存通道只能有一个插槽,因此,内存控制器与DDR3内存模组之间是点对点(Point-to-Point,P2P)的关系(单物理Bank的模组),或者是点对双点(Point-to-two-Point,P22P)的关系(双物理Bank的模组),从而大大地减轻了地址/命令/控制与数据总线的负载。而在内存模组方面,与DDR2的类别相类似,也有标准DIMM(台式PC)、SO-DIMM/Micro-DIMM(笔记本电脑)、FB-DIMM2(服务器)之分,其中第二代FB-DIMM将采用规格更高的AMB2(高级内存缓冲器)。

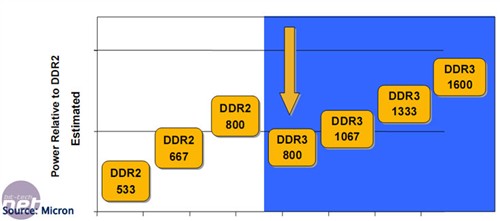

3. 采用100nm以下的生产工艺,将工作电压从1.8V降至1.5V,在DDR3系统中,对于内存系统工作非常重要的参考电压信号VREF将分为两个信号,即为命令与地址信号服务的VREFCA和为数据总线服务的VREFDQ,这将有效地提高系统数据总线的信噪等级。

4. 增加异步重置(Reset)与ZQ校准功能。重置是DDR3新增的一项重要功能,并为此专门准备了一个引脚。这一引脚将使DDR3的初始化处理变得简单。当Reset命令有效时,DDR3内存将停止所有操作,并切换至最少量活动状态,以节约电力。在Reset期间,DDR3内存将关闭内在的大部分功能,所有数据接收与发送器都将关闭,所有内部的程序装置将复位,DLL(延迟锁相环路)与时钟电路将停止工作,而且不理睬数据总线上的任何动静。这样一来,将使DDR3达到最节省电力的目的。

关注我们