HD5800辉煌的根本 RV870背后研发故事

迈入40纳米的代价

这部分内容几乎可以独立成章,但它对Cypress和整个EverGreen家族产品有直接影响,值得在这里说一说。

现在你可能已经听说台积电40nm工艺存在问题。这些问题现在已经解决,但是这些问题导致了Cypress芯片在去年可怜的产量和慢于预期的部署,它同样导致NVIDIA Fermi/GF100延迟。我下面想谈谈迈入40纳米工艺的事情,以及40纳米工艺为什么那么困难。

对无晶圆厂的半导体公司来说,最大的问题是,在新产品研发上,你必须对付一打供应商,比如显存厂商、元件制造商和知识产权厂商,你还必须处理与代工芯片生产商的关系。更糟的是,每一年左右,你的代工合作伙伴就会启用一个全新的进程让你使用。

代工厂商总是以相同的论调来说服你使用他们的新工艺,比如芯片尺寸更小,运行速度更快,能耗更低。你的代工合作伙伴总是希望你尽快购买其最新最贵的制程和工艺。他们要你在实际准备好之前,就掏钱购买他们的工艺。

但是,通常的情况是在你付钱之后,你的代工厂商会提出设计规则和提示清单给你,如果你遵循所有的准则,代工厂商就保证他们能够生产你的芯片。换句话说,做我们告诉你去作的东西,你的芯片就会量产。

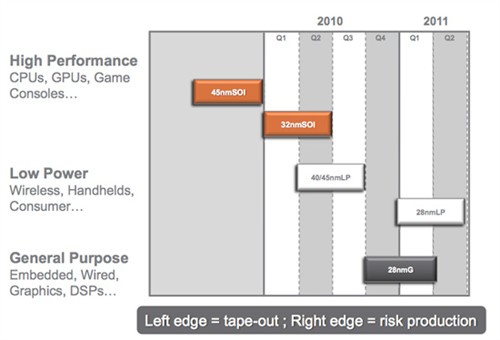

Global Foundries 2010年至2011年芯片工艺路线图

问题是,如果你遵循这些设计规则和暗示,结果是你的芯片在新工艺上的速度不会比旧工艺更快,产率也不会比旧工艺更高,但是你的成本会更高,因为你在设计芯片的时候轻信了代工厂商的暗示,让芯片面积膨胀。

一般工艺节点之间的晶圆大小不会改变。之前200毫米晶圆使用了很长时间,现在才进化到300mm晶圆。晶体管尺寸并没有缩小,因此从理论上讲,每代新工艺晶圆可以容纳更多的芯片。

任何新的制程都存在晶圆成本上升问题,这是由新制程复杂程度决定的。如果晶圆成本高出50%,那么你需要在每片晶圆当中至少多放入50%的芯片,才能让成本和旧制程持平。现实中,实际上想要多放入50%以上的芯片,因为需要考虑产率问题。如果你遵循代工厂商制定的保证产率的准则,你甚至不会接近收支平衡。

最终的结果是你从新制程当中的获益为零。这不是使用摩尔定律来获利的公司的选择,当然也不是GPU公司的选择。

这种问题的解决之道是,在你的公司有一些非常聪明的人,可以把代工厂商的这些设计规则和暗示归纳分析,并找出哪些可以忽略,以及如何解决剩下的规则和暗示。在这个领域当中,ATI和NVIDIA的做法有很大不同。

关注我们