台积电公布5nm工艺进度,未来产能将好于7nm

分享

衡量半导体工艺发展水平的一个关键指标,就是看它的量产芯片的产能。其中缺陷密度就与产能息息相关,任何半导体制造工艺的目标都是随着时间的推移将缺陷率降至低,从而为客户的订单提供更充足的产能。

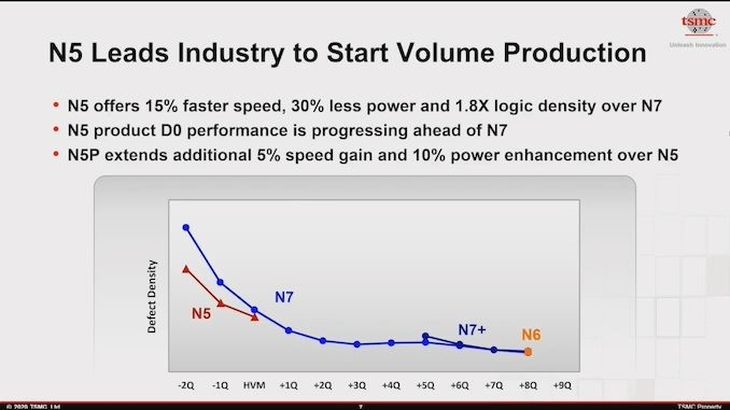

缺陷密度指的是每平方厘米的缺陷数量。低于0.5个缺陷/平方厘米的缺陷密度通常代表该工艺已经相当成熟,而台积电在2019年11月宣布其当时N7(7nm)工艺的缺陷密度已经达到0.09个单位。目前,人们习惯将新工艺的缺陷密度与同一时间的旧工艺缺陷密度进行比较,所以台积电在本周的TSMC技术研讨会放出了下面这张图表:

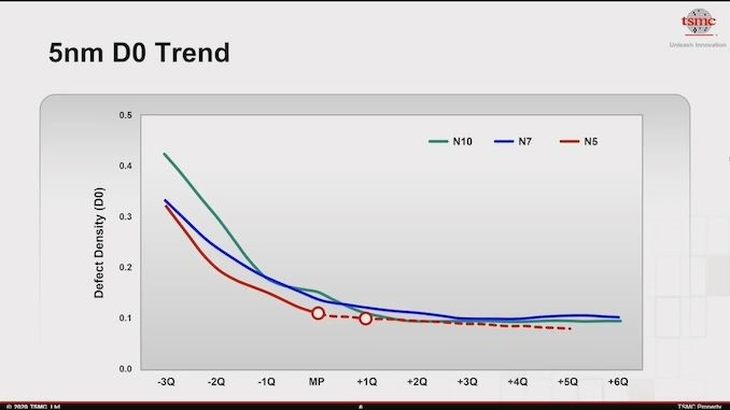

可以看出,目前台积电的N5工艺缺陷密度要比N7在开发周期的同一时间更低。晚些时候,他们又给出了更详细的线性图:

这意味着,台积电的N5工艺目前每立方厘米约有0.10-0.11个缺陷。同时,该公司预计,随着下季度大批量生产的增加,缺陷率将低于0.10。

5nm产能略微提高的部分原因可能是EUV(极紫外光刻)技术被越来越广泛使用。过去DUV技术需要4个步骤完成的制造,EUV用一个步骤就能取代,步骤的精简也就减少了缺陷产生的潜在风险。

基于台积电领先个5nm工艺(N5)的首批产品,预计会是今年晚些时候发布的智能手机处理器。

3人已赞

关注我们