内存之路在何方?DDR4代最新技术解读

泡泡网内存频道3月20日 三星电子公司宣布在上个月,已经完成了业界第一个DDR4内存模块的研发工作,并且使用30nm制程技术完成制作出样品。新DDR4内存模块可以在电压只有1.2伏特的情况下,达到2133MHz的运行速率,而且借助新的回路架构,DDR4可以上超3200MHz,三星说最终能达到4G。相较于DDR3,从低电压版的1.35V到正常电压的1.5V,在节能方面可以节省40%!

三星表示,这条DDR4内存使用了曾出现在高端显存颗粒上的“Pseudo Open Drain”(虚拟开漏极)技术,在读取、写入数据的时候漏电率只有DDR3内存的一半。

三星继成功研发出DDR、DDR2、DDR3内存后,现在又抢先推出DDR4,虽然DDR4的标准规格仍未定案,但是三星已经和多家内存厂商连手,帮助JEDEC固态技术协会“制订”DDR4的标准规格。JEDEC预计在2011年完成DDR4内存规范的制定工作,2012年开始商用,超过DDR3而成为主流规格则可能要等到2015年。

内存或许并不是很多玩家特别关心的内容。和显卡、主板等差异化较大的市场相比,内存市场由于有着强大的JDEDC把持,并且产品本身形态较为单一,因此各家产品性能和设计差距都不太大,同质化现象较严重。不过,同质化并不意味着发展速度慢,相反,也正是由于有了统一的JEDEC规范,内存一直按部就班地发展着。DDR4内存的消息最早出现在2007年,JEDEC展示了它们对未来DDR4内存发展的一些思考。在当时的新闻中,实验性的内容相当多,因此对最后内存规格的影响并不太大。如今,三年时间过去,DDR4内存再次浮出水面。这次我们看到了很多详细的内容说明,包括DDR4内存总线的变化以及频率、电压、工艺等相关问题。

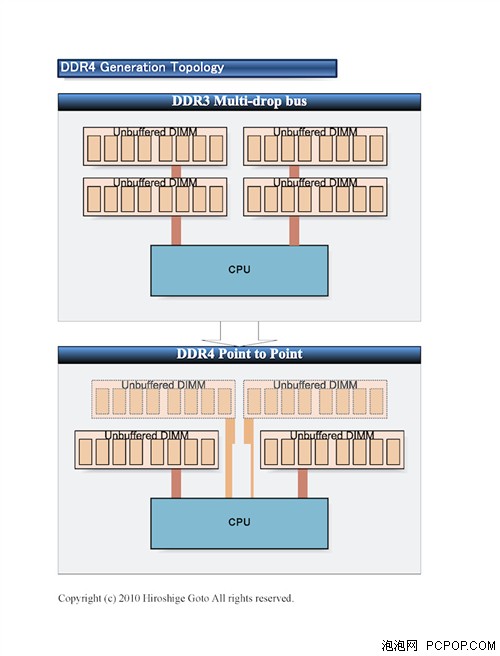

从DDR3的多点总线到DDR4的点对点技术

根据多位半导体业界相关人员的介绍, DDR4内存将会拥有两种规格。其中使用Single-endedSignaling信号( 传统SE信号)的DDR4内存其传输速率已经被确认为1.6~3.2Gbps,而基于DifferentialSignaling( 差分信号技术 )技术的DDR4内存其传输速率则将可以达到6.4Gbps。由于通过一个DRAM实现两种接口基本上是不可能的,因此DDR4内存将会同时存在基于传统SE信号和微分信号的两种规格产品。其中AMD公司的PhilHester先生也对此表示了确认。预计这两个标准将会推出不同的芯片产品,因此在DDR4内存时代我们将会看到两个互不兼容的内存产品。感觉似乎又要回到当年DDR内存与RAMBUS内存分庭抗礼的情形了。

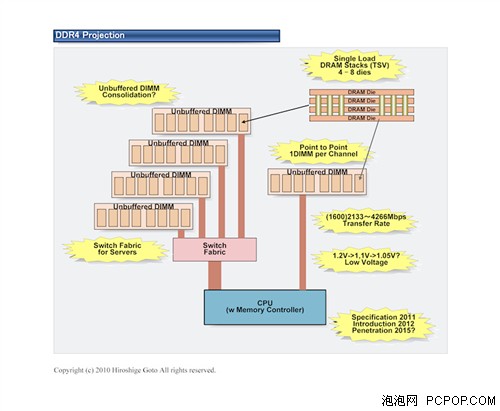

金邦曾透漏:承袭以往内存产品的发展走向,DDR4内存不外乎朝着高容量、高频、低功耗发展。它的规格可能在DDR4 2133~DDR4 4266,工作电压也将下降至1.0V~1.2V左右。这意味着DDR4内存在如此高频率、低电压的条件下运行,将需有更好的外部硬件设备来配合,否则容易造成内存数据遗失现象,以及消费者常遇到的兼容性问题。

依据目前JEDEC公布的数据看来,DDR4内存的每个内存信道只会支持一条内存模块,内存控制器将采用点对点技术,将取代目前DDR3内存采用的多点总线技术。如此一来,系统内存条的数量和容量都将受限制。因此在考虑如何增加系统内存数量与容量方面,将是DDR4内存后续生产在技术和成本方面需要重点考虑的地方。

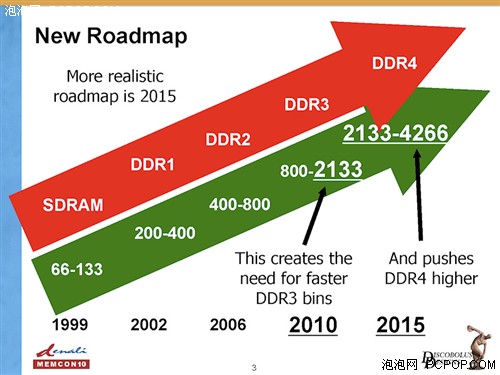

早在日本东京举行的MemCon 2010大会上,US Modular公司工程副总裁、JEDEC董事会成员Bill Gervasi介绍说,DDR4内存的有效运行频率初步设定在2133-4266MHz之间,运行电压则会进一步降低至1.2V、1.1V,甚至还可能会有1.05V的超低压节能版,生产工艺预计首批采用36nm或者32nm。

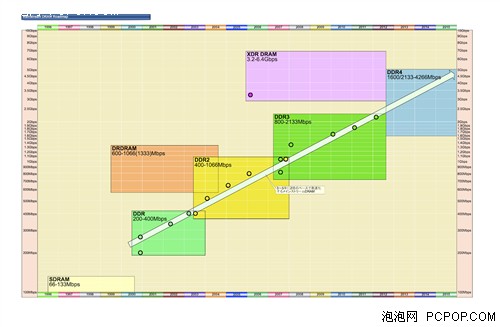

内存频率规格路线图

内存电压规格路线图

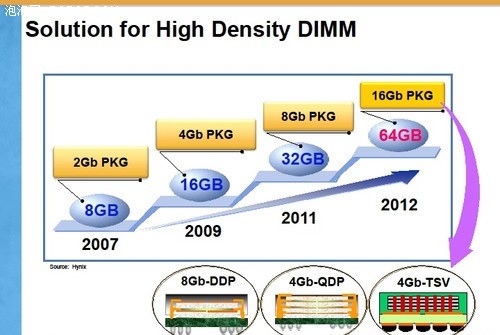

高容量内存的解决方法

很显然,这都是一年前的老消息了,09年的时候可是有媒体传言我们2011年就能用上DDR4内存了。那么现在DDR4内存的规则制定成什么样了呢?

DDR4内存规格预测图

JEDEC预计在2011年完成DDR4内存规范的制定工作,2012年开始商用,超越DDR3而成为主流规格则可能要等到2015年。

从DDR、DDR2到如今的DDR3,在提升频率、降低电压的同时,延迟也在不断变大。未来的DDR4带来的变化可能会变得更大。根据日本PCWatch专栏作家後藤弘茂分析称,DDR4时代每个内存通道只会支持一条内存模组,目前的多点总线将会被点对点技术所取代。这样导致的直接后果是系统可用内存条数量、容量都将受到影响。

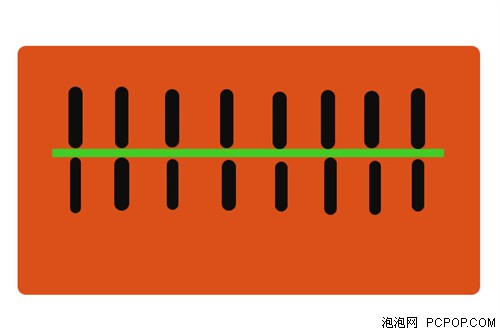

其实之前也有很多很多厂商推出了高容量的内存,例如去年三星曾经推出过一款32GB的服务器内存,由于采用多点总线技术可以在单个通道上无限制的怎么内存的颗粒数量,因为他们只需公用同一通道上的总线就可以了,当然考虑到内存体积的大小以及型号传输的延迟和干扰,内存颗粒数量还是会限制在一定的范围内。

三星去年发布的32GB内存

大容量内存多颗粒共用一个内存通道

为了解决这些问题,开发人员提出了两种解决方案:

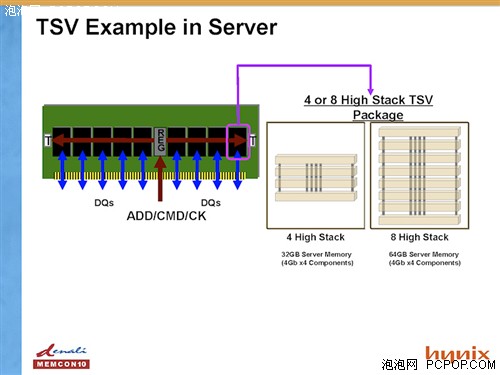

方案一:多层DRAM IC

多层DRAM IC

让DRAM厂商借助硅穿孔(TSV)技术和多层制造工艺,大幅提高单个内存颗粒的容量。这种方法的代价是对DRAM生产技术提出非常高的要求,致使内存价格狂飚几乎是可以预见的。同时用户也会比较麻烦,为了提高多通道性能必须在升级时同时替换所有内存条。DDR4会尝试使用硅穿孔(TSV)技术来提升容量密度。

比如普通单层封装可以制造单条容量8GB的内存,四层封装就可以让容量翻两番到32GB,八层封装则可以达到64GB的惊人容量。不过这对生产工艺要求很高,良品率在短时间内很难得到保证。因此很可能会大幅度提高内存的成本和销售价格,对DDR4的推广来说是非常不利的。

方案二:多内存共用通道

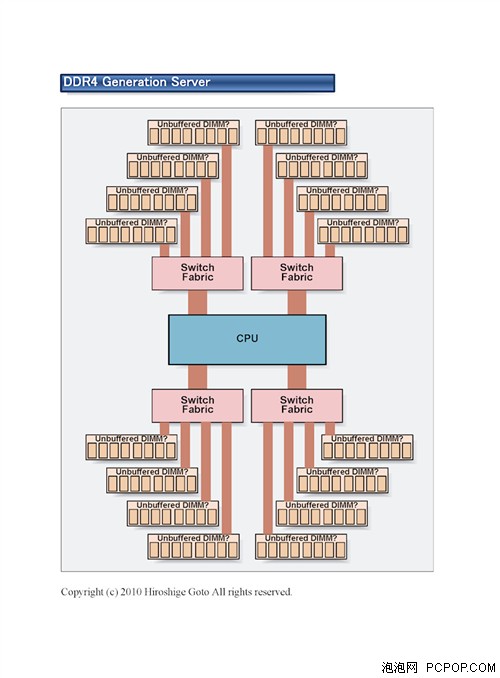

DDR4可能会在服务器上使用切换开关来扩大每通道容量

Digital Switch数字开关

芯片厂商还可以设计一颗“Digital Switch数字开关”起到“桥”的作用。这颗“桥芯片”一边连接内存,一边连接内存控制器。它连接内存的一端,类似传统的多点分支总线的作用,将很多内存的容量扩展相加,实现高容量;连接内存控制器的一端则固定位宽。内存控制器不会在意连接的设备是什么,它只需要连接在总线上的设备达到要求即可。DDR4内存控制器会将“桥芯片”和多条内存看作一整个大容量的内存,从而实现正常运作。

不过额外添加桥接芯片的方式也有自己的问题。额外桥接会导致性能损失、延迟变大,并且桥接芯片是否能完整保障每个内存的兼容性,桥接芯片对总的内存传输带宽不会有显著的提高,内存容量则可以成倍提高,其设计原理和多层DRAM IC类似,不过就是减少了内存所需的带宽布线,但传输的数据也不如多层DRAM IC多,桥接芯片可能采用的是分时复用或者是动态分配,那样的话设计成本会增加非常多,而且在高速传输过程中可能会影响传输性能,这都将是未来研发的重点。

在服务器领域,如果多层DRAM IC方式不适合,那只能在主板上做手脚了。比如可以在主板上安装特殊的控制器,允许多个内存条工作在同一内存通道内。这样做的后果也有很大的潜在问题,比如增加了主板的制造成本和技术要求、限制了内存性能发挥,另外还会造成潜在的兼容性问题。DDR4可能会在服务器上使用切换开关来扩大每通道容量。

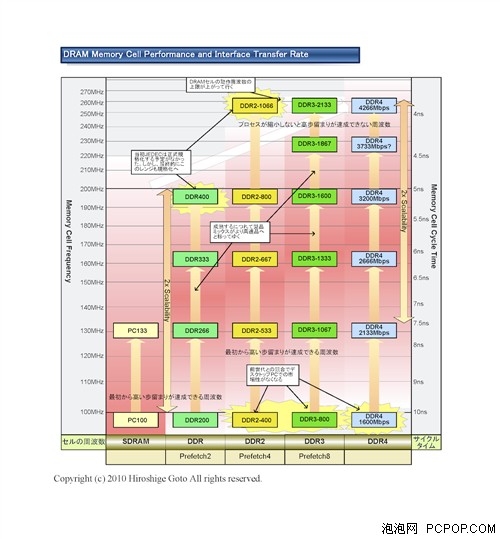

从早期的SDR内存到现在的DDR3内存,内存的技术不但变化,内存的电压降了不少,工艺也提升了不少,但是内部的运行频率变化基本没有什么变化。

不同时代内存频率、电压、功耗关系图

DRAM内存总体规格路线图

DRAM制造工艺路线图

DRAM内存单元频率和循环时间关系图

目前Intel与AMD的CPU产品都在内部整合了内存控制器,如果DDR4问世,那么CPU必须要变化,新的信号传输方式甚至会引起CPU接口的转变,而与之配合的主板产品亦会应为生产线的更新而大幅提升成本。到时候采用DDR4内存的电脑无疑还是会像i7+X58+DDR刚刚问世时一样——成为个别有米一族的玩物。 ■ <

关注我们