手机和平板的芯:ARM处理器前身今世

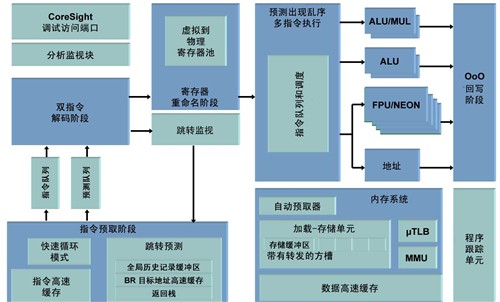

Cortex-A9是目前为止性能最高的ARM处理器,可实现受到广泛支持的ARMv7体系结构的丰富功能。相对Cortex A8,新的Cortex 9可以最多设计四个处理内核,Cortex-A9处理器的设计旨在打造非常先进的、高效率的、长度动态可变的、多指令执行超标量体系结构,提供采用乱序猜测方式执行的8阶段管道处理器,凭借范围广泛的消费类、网络、企业和移动应用中的前沿产品所需的功能,它可以提供比较独特的高性能和高能效。

Cortex-A9微体系结构既可用于可伸缩的多核处理器(Cortex-A9 MPCore多核处理器),也可用于更传统的处理器(Cortex-A9单核处理器)。可伸缩的多核处理器和单核处理器支持16/32/64KB 4路关联的L1高速缓存配置,对于可选的L2高速缓存控制器,最多支持8MB的L2高速缓存配置,它们具有极高的灵活性,均适用于特定应用领域和市场。

- 非常好的性能,2GHz标准操作可提供TSMC 40G硬宏实现

- 以低功耗为目标的单核实现,面向成本敏感型设备

- 利用高级MPCore技术,最多可扩展为4个一致的内核

- 可选NEON媒体和浮点处理引擎

风靡Android的Tegra 2采用了Cortex A9双核架构

通过共享以下常见需求,Cortex-A9处理器可提供满足各种不同市场应用需求的可扩展解决方案,包括移动手机以及高性能的消费类产品和企业产品:

- 通过提高性能、降低功耗来提高能效;

- 提高最高性能,满足要求更高的应用需求;

- 能够在多个设备之间共享软件和工具投资;

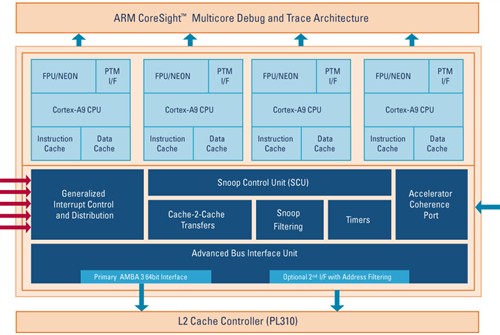

Cortex-A9 MPCore多核处理器

Cortex-A9 MPCore集成了经验证非常成功的ARM MPCore技术以及更多增强功能,以此简化了多核解决方案,并使其应用范围得到扩展。Cortex-A9 MPCore处理器可提供比较独特的可扩展的最高性能,同时还支持灵活设计和新功能,从而进一步降低和控制处理器和系统级的能耗。借助Cortex-A9 MPCore 处理器的定向实现,移动设备的最高性能还可在现在的解决方案的基础上不断提高,具体方法是:利用设计灵活性和ARM MPCore技术提供的高级功率管理技术,在散热受限以及移动电源预算紧张的情况下维持运行。使用可伸缩的最高性能,该处理器可超过现今类似的高性能嵌入式设备的性能,并可在拓宽市场的基础上进行稳定的软件投资。

Cortex-A9单核处理器

Cortex-A9处理器提供了比较独特的高性能和高能效,从而使其成为需要在低功耗、成本敏感、基于单核处理器的设备中提供高性能的所有设计的理想解决方案。使用便利的可合成流和IP成品,Cortex-A9处理器可为基于ARM11处理器的现有设计提供理想的升级途径,这类设计需要在相似的硅成本和电源预算基础上提供更高的性能和更高级别的能效,同时使软件环境保持兼容。Cortex-A9单核处理器为独立指令和数据事务提供了双重、低延迟、Harvard 64位AMBA 3 AXI主接口,在内存的缓存区域之间复制数据时,它能够维持每五个处理器周期执行四次双字写入。

除了单核和多核软宏外,常用的双核配置也可用作TSMC 40G/GL工艺的硬宏实现,从而最大程度地缩短高性能Cortex-A9处理器的上市时间,降低与其上市关联的风险和成本。利用优化的ARM物理IP和先进的实现技术,该硬宏可用作功率优化实现或性能优化实现。

速度优化:速度优化硬宏实现可向系统设计人员提供行业标准ARM处理器的整合低功率技术,从而使ARM的性能领先优势进一步延伸到紧凑、高密度和散热受限的环境所需的功率包络中的高利润消费类设备和企业设备。从标准硅中选择该硬宏实现后,它的运行频率超过2GHz,代表了面向性能的高利润应用中的理想解决方案。

功率优化:在许多散热受限的应用领域中,能效极为重要。从标准硅中选择Cortex-A9功率优化硬宏实现后,其提供的最高性能达到4000DMIPS,而每个CPU的能耗不到250mW。

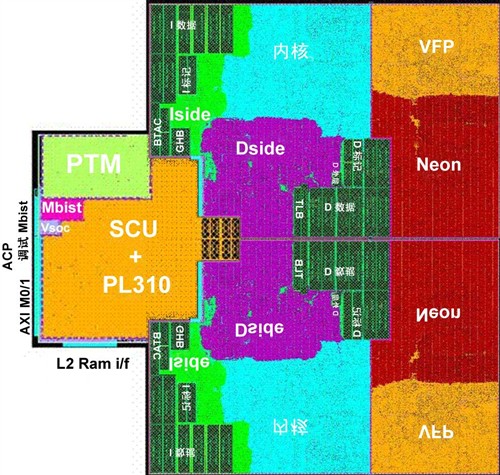

该硬宏实现包括符合ARM AMBA标准的高性能系统组件,可以最大程度地提高数据通信速度,同时使能耗和硅面积降到最低。各Cortex-A9硬宏实现还包括CoreSight程序跟踪宏单元(PTM),它使处理器的指令流完全可见,从而使软件社区成员能够开发优化性能的代码。此外,该宏还包括ARM高性能L2高速缓存控制器,它支持L2高速缓存内存介于128K和8M之间的配置。

典型芯片代表:

德州仪器:OMAP 4430/4460/4470

高通:MSM 8260/8660、APQ 8060/8064

NVIDIA:Tegra 2

苹果:A5

关注我们