摩尔定律不死!Intel双核心深入剖析

在服务器平台,现有的双路至强(Xeon DP)平台将从2006年起导入Dempsey处理器,配合E7520芯片组构成Bensley平台。Dempsey处理器在结构和特性上类似于Presler,接口则采用LGA 771。

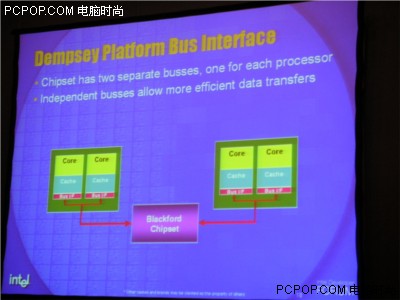

Bensley平台采用了双总线结构,每颗Dempsey处理器通过一条独立的总线和E7520芯片组通信,而在处理器内部,每个核心仍葆有独立的总线接口。Inkley先生表示,独立的总线将带来更高效的数据传输。

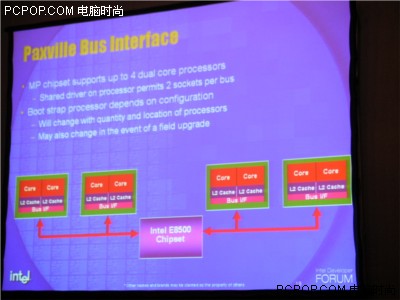

更高端的多路至强(Xeon MP)平台则将由Paxville处理器搭配E8500/E8850芯片组构成Truland平台。尽管计划在2006年第一季度推出,Paxville处理器仍然采用90nm工艺而不是更“新潮”的65nm。它支持HTT、EM64T和XDB,接口类型不详。

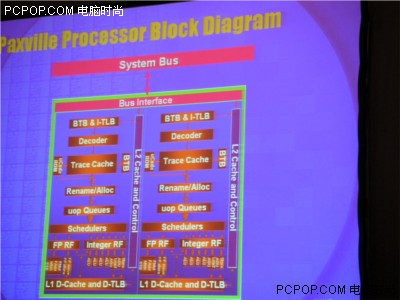

Truland和前面介绍的所有平台最大的不同,乃是Paxville的两个核心的总线接口合二为一,采用了共享总线的模式。由于Truland平台支持最多4颗Paxville处理器,而每颗处理器又包含两个独立的核心,再加上超线程技术派生出的逻辑处理器,Truland平台将拥有最多16个逻辑处理器!Inkley先生表示,考虑到总线和芯片组物理上的负荷能力,E8500芯片组允许在每条总线上有最多两颗处理器——这就是性能和设计能力折中的结果。

Inkley先生解释道,如果像Bensley平台那样,每颗处理器都使用一条独立的总线,那么E8500芯片组需要提供最多4条总线来和处理器通信,这在芯片组本身和主板的设计上都存在很大的困难;而如果4颗处理器共用同一条总线,一方面系统性能将低到不可接受,另一方面这条总线的负载也绝非目前芯片组和主板的设计水平所能满足。

因此,在处理器内部将两个核心的总线接口整合,再通过共享总线的方式来取得性能和设计上的均衡,就构成了Xeon MP在双核心时代的第一步,而层层整合的总线是否会影响双核心Xeon MP平台性能的发挥,目前我们还不得而知。

至于多处理器的仲裁,也就是由哪颗处理器担当Boot strap来引导系统,则根据处理器的数量和位置有所不同,并且还会随处理器版本升级而改变——如果某一颗处理器的Stepping版本更新,则系统会将它识别为Boot strap。

曾经寄托了Intel 64位运算神话的安腾(Itanium)平台也将在今年第四季度迎来双核心的Montecito处理器,它采用90nm工艺,支持4组并发线程,拥有两个1MB的二级指令缓存和两个13MB的三级缓存——这样它内核外部的缓存容量就将达到空前的28MB,其晶体管数量也高达172000万个!

关注我们