摩尔定律不死!Intel双核心深入剖析

双核心来了。就像2002年的第一场雪,Intel在桌面平台推动多核心处理器的进程,来得比所有人的预计都要早一些。在2005年3月1日~3月3日的春季IDF上,Intel一反最近几年的保守态度,非常积极地介绍了从高端服务器的Itanium直到移动计算平台的全系列双核心处理器产品规划,并且现场展示了双核心处理器的实物以及演示平台。

2005年4月14日~4月15日,在北京的春季IDF会议现场,我们终于亲眼见到了Intel双核心处理器的实物,同时也有幸深入了解了Intel在双核心乃至未来多核心处理器方面的规划。

短短4天之后,北京时间2005年4月19日,Intel在美国率先发布了双核心Pentium至尊版处理器Pentium D 840,Dell、HP等PC厂商也同步推出配备Pentium D 840处理器的台式机。

——当然,这一切都要归功于AMD。如果不是AMD x86-64平台在2003年~2004年间的巨大成功在使Intel出现一系列失误的同时不得不修正对64位平台普及时间表的预估;如果不是AMD的64位处理器在高端服务器和主流桌面平台不断蚕食Intel的市场份额;如果不是AMD高调力推双核心处理器,Intel现在大概还在稳稳当当为4GHz的Pentium 4处理器做宣传,准备到第三季度再发布双核心处理器吧。

有竞争才有进步,双核心时代的提前揭幕再次证明了这一点。

就在Intel正式发布Pentium EE 840之前,在2005年4月14日~15日北京春季IDF会议的现场,我们有幸目睹了基于这款产品的演示平台,并且通过Intel的介绍和讲解,对双核心处理器的产品线分布有了更加深入的了解。

得益于平台策略的全面推行,双核心/多核心的话题在几乎每一场的主题演讲中都被提及,无论是作为“开场白”的前任CTO Pat Gelsinger的《创新之路》,还是移动事业部总经理浦大卫的《移动时代》,乃至数字家庭事业部副总裁兼消费电子事业部总经理格琳达·多柴克的《数字家庭进入千家万户》和数字企业事业部商用客户机部总经理罗伯特·克鲁柯的《数字企业》,无不将双核心作为重点之一。

而在英特尔公司高级院士兼英特尔通信技术实验室总监凯文·康的《想像未来……2015年的平台》中,从多处理器到超线程技术,从双内核、4内核到32内核,越来越多的内核将被集成到未来的处理器中,而运算平台的并行程度也将随之出现巨大的飞跃——站在2005年的春天看未来,Intel告诉我们,未来的处理器必然会包含越来越多的内核,而摩尔定律关于“芯片所集成的晶体管数量每18个月就将翻一番”的预言,也将在Intel制程技术的保障下至少再走10年。

这样的预言和两年、乃至一年以前Intel在IDF上为我们描绘的图景有了很大的不同。那时候,Intel似乎更加热衷于告诉我们未来处理器的频率将会飙升到何其惊人的数字:4GHz、5GHz、10GHz……仿佛追随摩尔定律增加的晶体管都是为了提升频率而存在的。

但是今天,在Intel终于回归用架构、性能作为划分产品系列的标准之后,我们看到,摩尔定律为芯片增加的晶体管除了提高频率之外有了更利于提升性能的用途——集成更多核心。

2005年4月15日下午,在以双核心处理器为主题的技术讲座中,Intel处理器应用高级工程师Benson Inkley先生为我们揭示了Intel在台式机、工作站和服务器方面的双核心规划,并且剖析了双核心、超线程在工作方式以及性能表现等方面的不同。

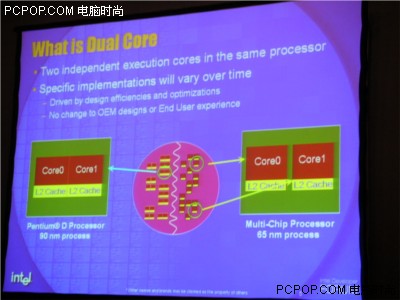

Benson Inkley先生首先向我们讲解了双核心不同的物理结构——并列双核心与分离双核心(说明一点,这是笔者总结出来的称呼,并非Intel官方说法)。

在90nm的Pentium D处理器中,两个物理核心紧密相连,分别拥有各自独立的内核及二级缓存。而在未来的多芯片处理器中,两个(或者更多)核心分离排布同样拥有各自独立的内核及二级缓存——Inkley先生表示,这种结构将应用于65nm工艺的多核心处理器中。而在65nm之后,Inkley先生表示,也许这些分离的核心又将连结到一起,回归Pentium D的结构,这样做的原因,则是出于设计效率和优化方面的考虑(通俗一点就是良率),对于最终用户来说,他们看到的其实都是一样的处理器——一片盖着金属盖子的覆晶材料基板。

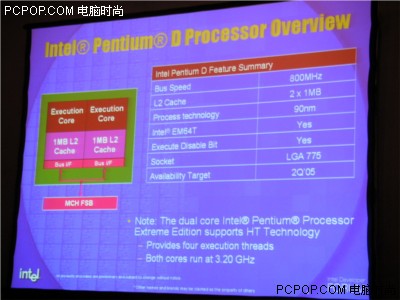

最先与我们见面的,也就是4月19日正式发布的,乃是桌面级的Pentium D处理器家族,它包括2.8GHz的Pentium D 820、3.0GHz的Pentium D 830和3.2GHz的Pentium Extreme Edition 840,它们的FSB都是800MHz,拥有两个独立的1MB二级缓存,支持Intel EM64T 64位扩展技术和基于底层安全技术的Execute Disable Bit(XDB)技术。和现在的90nm Pentium 4处理器一样,Pentium D采用LGA 775接口。

在Pentium D家族中,惟一不同的是Pentium EE 840,它支持超线程技术,开启后能在两个物理核心的基础上实现4颗逻辑处理器,进一步提高系统的并行程度。在IDF的现场,我们看到了基于Pentium EE 840的演示平台。从Tt机箱透明的侧板看进去,我们看到Pentium EE 840的散热系统相当硕大。

这个演示平台仍然是32位的Windows XP Professional+SP2的操作系统,没有安装什么软件。通过操作系统的任务管理器,我们可以看到系统中有4颗逻辑处理器,频率都是3200MHz。当通过Intel提供的Maximum Power Program for SmithfieldXE Processor软件将两个核心的负载都提升到100%时,我们看到4颗逻辑处理器都在满负荷运行;将核心0的负载降低到50%后,我们看到整体的CPU占用变成了75%,核心0的一颗逻辑处理器满负荷运转,而另一颗则处于空闲状态——由此我们也看到了现有操作系统在线程调度方面的大致表现。

另一个双核心演示平台则通过繁重的视频压缩任务来体现多核心并行处理的优势。用Adobe Premiere Pro同时压缩两段视频剪辑,现在看来似乎是Mission Impossible,但是对于开启超线程的Pentium EE 840平台,这样的任务却显得异常轻松。

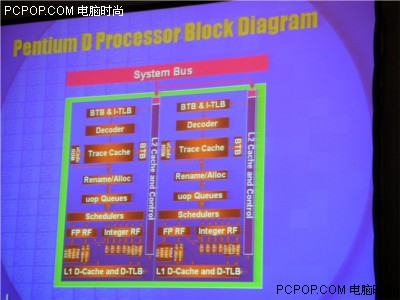

和现有的Pentium 4处理器相比,Pentium D在核心架构上并无不同,只是包含了两个Pentium 4的核心,并且提供独立的总线接口。因此,在多指令并行处理方面,Pentium D将具有比Pentium 4更高的效率,而如果是为超线程技术优化的同时包含整数和浮点运算的多指令并发执行,则Pentium EE 840的性能将得到最充分的发挥。

这里要针对Pentium D的命名替Intel进行一些澄清。Pentium D这个名称甫一出现,有关“D”的含义的猜测就接踵而至,归纳起来,一种认为“D”代表了“DualCore(双核心)”的意思,另一种则认为“D”代表“Desktop(桌面)”——就像Pentium M中的“M”可以理解为“Mobile”一样,还有一种推测则基于“D”是字母表中第四个字母,因此是Pentium 4的新写法……

技术讲座结束之后我们专程就这个问题请教了Benson Inkley先生,他的反应看起来显得有些困惑:“我们并没有赋予它(D)任何特定的意思,Pentium D就是Pentium D,一个代号而已,它不代表任何含义。”在了解到我们对“名分”的重视之后,他对这种猜测表示了理解:“Pentium D不代表任何含义,当然,从反面来说,你可以赋予它任何的含义。”——这就是Intel对Pentium D命名的官方解释。

在90nm的Smithfield之后,65nm的Presler核心将以分离双核心结构登场,这种结构的好处在于能够用任意单核心进行组合,从而提高良率。在架构方面,构成Presler核心的每个独立的Cedar Mill内核都会将二级缓存容量提升到2MB,同时支持HTT、EM64T和XDB,仍然沿用LGA 775接口,除此之外,就Presler和Pentium D的结构框图对比而言,我们还看不到更多的改进——从这里我们可以看出,目前的Pentium 4处理器的下一个内核自然非Cedar Mill莫属了。

对于一些媒体在介绍双核心时提到的将两颗核心的二级缓存合并而产生的共享二级缓存的双核心处理器版本,Inkley先生予以了否认。他表示,目前Intel并没有规划这类产品——当然,也许这样的设计会在未来的产品中出现。由于这种结构涉及到二级缓存的命中率问题,Inkley先生进行了进一步的解释,无论Smithfield还是Presler,独立的二级缓存之间都有数据通道相连,如果核心0需要的数据恰巧位于核心1的二级缓存中,那么这个数据将可以很快被复制到核心0的二级缓存里,以供核心0调用。

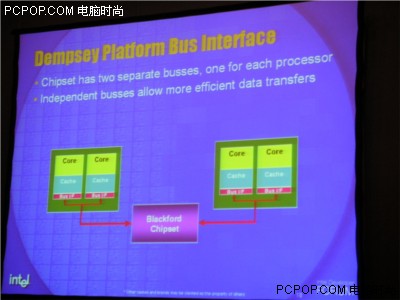

在服务器平台,现有的双路至强(Xeon DP)平台将从2006年起导入Dempsey处理器,配合E7520芯片组构成Bensley平台。Dempsey处理器在结构和特性上类似于Presler,接口则采用LGA 771。

Bensley平台采用了双总线结构,每颗Dempsey处理器通过一条独立的总线和E7520芯片组通信,而在处理器内部,每个核心仍葆有独立的总线接口。Inkley先生表示,独立的总线将带来更高效的数据传输。

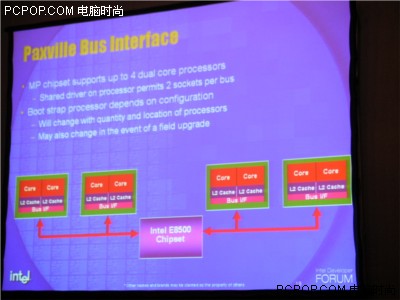

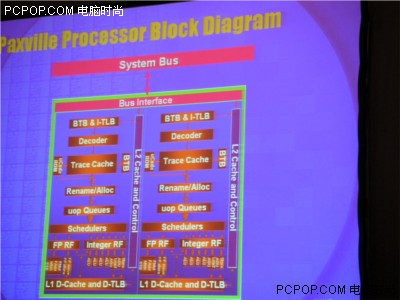

更高端的多路至强(Xeon MP)平台则将由Paxville处理器搭配E8500/E8850芯片组构成Truland平台。尽管计划在2006年第一季度推出,Paxville处理器仍然采用90nm工艺而不是更“新潮”的65nm。它支持HTT、EM64T和XDB,接口类型不详。

Truland和前面介绍的所有平台最大的不同,乃是Paxville的两个核心的总线接口合二为一,采用了共享总线的模式。由于Truland平台支持最多4颗Paxville处理器,而每颗处理器又包含两个独立的核心,再加上超线程技术派生出的逻辑处理器,Truland平台将拥有最多16个逻辑处理器!Inkley先生表示,考虑到总线和芯片组物理上的负荷能力,E8500芯片组允许在每条总线上有最多两颗处理器——这就是性能和设计能力折中的结果。

Inkley先生解释道,如果像Bensley平台那样,每颗处理器都使用一条独立的总线,那么E8500芯片组需要提供最多4条总线来和处理器通信,这在芯片组本身和主板的设计上都存在很大的困难;而如果4颗处理器共用同一条总线,一方面系统性能将低到不可接受,另一方面这条总线的负载也绝非目前芯片组和主板的设计水平所能满足。

因此,在处理器内部将两个核心的总线接口整合,再通过共享总线的方式来取得性能和设计上的均衡,就构成了Xeon MP在双核心时代的第一步,而层层整合的总线是否会影响双核心Xeon MP平台性能的发挥,目前我们还不得而知。

至于多处理器的仲裁,也就是由哪颗处理器担当Boot strap来引导系统,则根据处理器的数量和位置有所不同,并且还会随处理器版本升级而改变——如果某一颗处理器的Stepping版本更新,则系统会将它识别为Boot strap。

曾经寄托了Intel 64位运算神话的安腾(Itanium)平台也将在今年第四季度迎来双核心的Montecito处理器,它采用90nm工艺,支持4组并发线程,拥有两个1MB的二级指令缓存和两个13MB的三级缓存——这样它内核外部的缓存容量就将达到空前的28MB,其晶体管数量也高达172000万个!

关注我们