轻松读懂移动处理器 CPU微架构全解析

分享

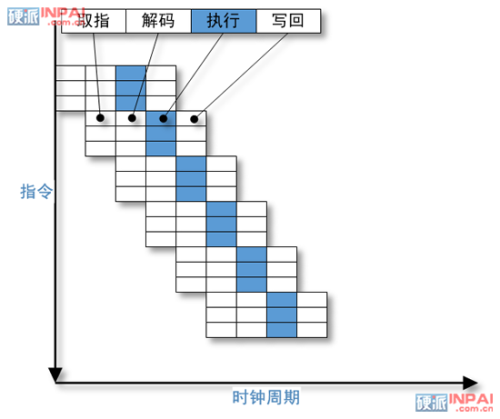

既然流水线设计可以实现不间断取指、解码、执行、写回,那为何不干脆同时做几条流水线一起取指、解码、执行、写回呢?这就引出了超标量设计。

上图就是一个三路超标量四工位流水线的指令/周期执行示意图,可以看到 CPI 从 1 变成 0.33,即每周期执行 3.33 条指令,这样的改进幅度是令人着迷的,因此在初期的时候超标量甚至被人们赞美为标量程序的向量式处理。

不过在现实中不可能都这样,因为现在的处理器执行不同指令时候的“执行”段工位并不完全一样,例如整数可能短一些,浮点或者向量和 Load/Store 指令需要长一些,加上一些别的因素,实际大部分程序的实际 CPI 都是 1.x 甚至更高啊。

例如:

a = b * c

d = a + 1

这里的第二条指令需要使用到第一条指令的计算结果,因此必须等待第一条指令完成后才能跑第二条指令,更重要的是,在不少处理器上乘法指令并非一个周期而是需要多个周期才能完成。在遇到这样的情况时,就不能实现多指令发射而且会出现流水线停顿。

2人已赞

第1页:什么是应用处理器?第2页:长话短说“微架构”——流水线第3页:长话短说“微架构”——超标量第4页:长话短说“微架构”——分支(转移)预测第5页:长话短说“微架构”——动态调度第6页:长话短说“微架构”——线程级并行化第7页:长话短说“微架构”——数据级并行(SIMD)第8页:长话短说“微架构”——存储系统分层结构第9页:ARM 指令集架构的由来第10页:ARM Cortex-A9 内核微架构特点第11页:ARM Cortex-A15 内核微架构特点第12页:高通 Krait 内核微架构特点第13页:苹果 Swift 内核微架构特点第14页:英特尔 Bonnell/Saltwell 内核微架构特点第15页:ARM Cortex-A5/Cortex-A7 微架构的特点第16页:移动图形处理器形势简话第17页:PowerVR SGX 54x MP4 GPU 微架构第18页:全文总结

关注我们