终极指南:2013年手机CPU的现状与未来

通过改进处理器微架构来获得性能提升是最体面的方法,也是最难的方法。从40年前的英特尔4004,再到今天的酷睿i7,IPS(每周期指令吞吐量)也就是从1提升到2再提升到3的进步。再往上,就撞到了难以逾越的功耗之墙。

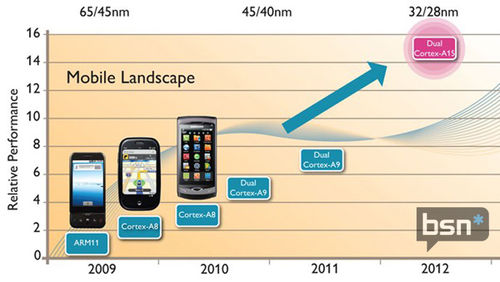

如何打破这堵高高的墙壁?答案只有一个:更好的工艺。对于ARM而言尤其如此。5年前的ARM11处理器还在使用老掉牙的130nm普通CMOS工艺。而最近一到两年,由于无法从核心上榨取更多的油水,业界开始用越来越新的工艺制作非常先进的ARM处理器,从45nm到32nm甚至现在的28nm,ARM处理器在工艺上的进步速度要远超同期PC处理器。正是这些新工艺,支撑着ARM处理器在近几年内以每年200%的速度在提升。

但是提到工艺,我们就不得不再一次提到一个词:极限。没错,通过超量应用工艺,我们获得了超量的性能提升,但是工艺的储备并不是无穷无尽的,现在的我们已经走在了工艺的极限上。如果是传统的工程极限,随着新技术和新方法的发明,最终都可以实现突破,但是工艺面临的这道极限的背后是物理定律。

在28nm以后,晶体管实在是太小了,小到我们必须重新梳理物理定律,才能准确掌握它的物理性质。随着半导体工艺线宽迈入20nm以下,集成电路中的某些结构已经开始迈入介观和微观之间的灰色地带。对于微观世界,也就是量子世界,人们目前所掌握的物理学,并不能给出太多具备足够工程价值的答案。

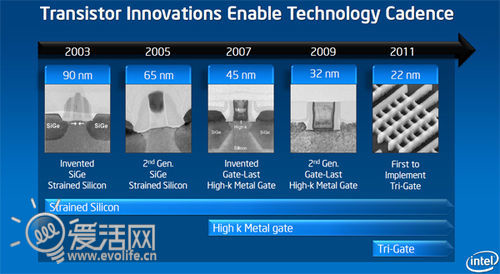

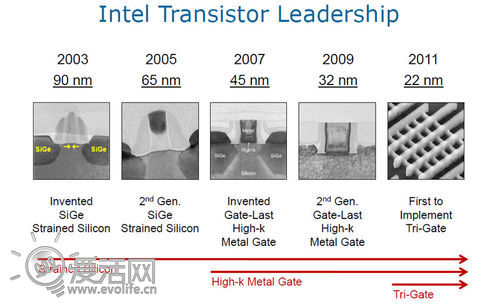

也许你很难想象,现代为处理器所使用的晶体管,其栅极漏电的很大一部分原因已经是量子隧穿效应。这是因为对于一个线宽只有30nm的晶体管而言,它的栅极绝缘材料的厚度只有不到2nm,也就是说,只有不到10层原子的厚度。而工艺非常先进的英特尔,其量产晶体管的栅极绝缘层厚度已经不到1nm,只有5层原子的厚度。在这样的规模下,宏观的物理定律已经有相当程度的失效,这个规模的晶体管会做出什么行为?更多的只能靠猜测,靠无数次的实验。

当经典物理定律失效,人们需要在盲目的实验中找到解决方案时,进步的速度就变得不再可以预测。

单个晶体管的绝缘层厚度已经只有数十层原子

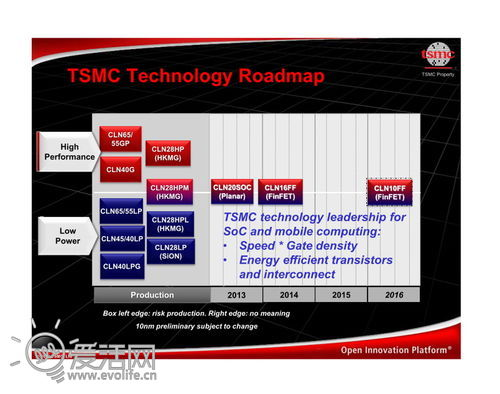

2013年已经是28nm的时代,按照预测,2014年业界就将往20nm迈进。但是这一步能顺利走出去么?相信没人对此能有足够的信心。作为世界上最大的代工厂,台积电TSMC的工艺路线对于业界的影响力是最为巨大的,早在2009年,TSMC就已经宣布将要量产28nm逻辑电路工艺,但是实际情况是直到2011年底,TSMC都没能拿出哪怕只用于性能测试的样品芯片,而最终的量产一直到2012年6月才在跌跌撞撞中开始,前后延期达三年。那么,面对TSMC“2013年底量产20nm”的豪言壮语,你又能相信多少呢?

台积电早先公布的路线图,回头来看雄心壮志基本停留在纸上

TSMC的下一代20纳米工艺还面临一个问题——性能提升将非常有限。从官方演示文档中我们可以看到,TSMC的20nm规划中,针对移动设备的工艺——也就是LP、HPL和HPM——被整合成了一种,名为20SoC。它的性能,以TSMC官方的预计,仅能实现漏电比28HPM降低20%、性能比28HPM提升15%的水平。希望各位注意,对比的对象是28HPM,而28HPM的漏电水平与28LP是接近的,也就是说从28nm到20nm,TSMC只实现了20%的漏电降低。

这是官方最乐观的预计,而实际情况可能要比这个悲观的多,一如TSMC对于28nm量产时间的预计一样。那么我们就可以得到一个自然而然的预计:20nm时代,我们除了更高的集成度,什么都得不到。这就意味着,以20nm工艺制造的芯片,固然可以通过规模的扩大而获得更大的理论性能,却几乎无法从工艺的进步得到单位功耗效率的提升。在目前手机处理器绝对性能已经超过体效值的大前提下,这样的结论几乎就已经宣布了,未来的产品不会为我们带来更快的实际性能。

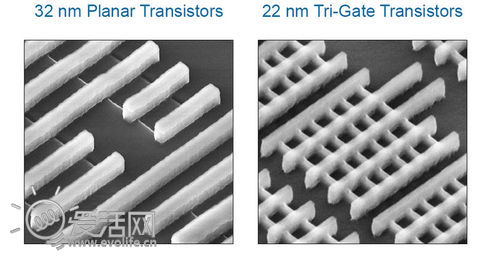

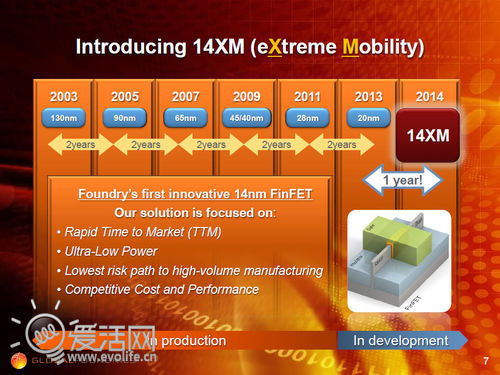

英特尔在2012年开始量产3D晶体管,台积电至少要等到2015年

那么更先进的工艺呢?例如16nm?根据目前的规划,TSMC将在16nm引入近年来半导体工艺中继HKMG后最大也可能是最后的进步,也就是3D晶体管,又叫finfet。这个技术可以为单个晶体管带来40%的性能提升,同时降低30%的功耗,目前已由英特尔量产,而整个业界只有英特尔实现了量产,由此可见其技术难度水平。我们没有理由认为,TSMC对于finfet的引入会一帆风顺,外加16nm对于EUV的需求以及EUV产业目前的状况,至少在笔者看来,TSMC可以在2015年量产16nm finfet的概率几乎为0。至于GlobalFoundries或者三星,前者目前刚刚实现28nm的量产,虽然幻灯片已经写到了10nm,但是我们不应对其抱有太大的信心,而三星的产能过小,即便有良好的工艺,也无法支撑业界的需求,因此不需要投以太大的注意力。

这就意味着,2014年和2015年对于ARM而言会非常艰难。因为先进工艺在这两年将出现空窗期,而没有先进工艺的支持,ARM系产品的性能进步就只能停留在纸面。当然,也有一种选择,那就是提前在20nm上——就像英特尔所做的那样——引入finfet,但这会给本来就已充满变数的20nm工艺增添新的难度,最极端情况下也许会导致2014年的彻底空白。因此我们似乎必须接受2014到2015年的空窗期。

那么,更先进,比16nm还先进的工艺呢?业界普遍认为,由于物理规律限制,目前常规晶体管的极限将在2nm左右到来,在这个规模下,基于宏观原理工作的硅基半导体晶体管将彻底无法运行。而考虑到工程实际情况,也许在10nm时就已经会遭遇无法解决的问题。所以保守来说,我们依靠了40年,并以之建立了辉煌信息产业大厦的硅基半导体工业,也许在10年内就会走到尽头,我们所剩下的工艺,乐观估计还有6代,悲观估计可能只有4代。之后,人们就必须要想办法去寻找新的原理,以新的材料制造新的器件。突破终将会到来,但是究竟需要多长时间?谁也没把握,因为基础物理已经80年没有进步了,半导体行业在打光手中所有牌之后的痛苦空白期到底有多长,没有人可以给出答案。

关注我们