架构变革! 深入研究"扣肉"与内存时序

分享

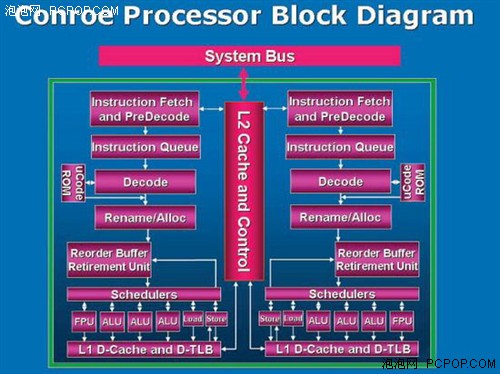

从SD内存时代开始,如何通过优化内存时序来提升系统性能,便已成为众多超频发烧友津津乐道的话题。从SD到DDR以至如今风头正劲的DDR2,内存延时始终是不可能避免的,而且大家普遍认为这个延时当然是越短越好。不过,随着近期国内外各大网站针对Intel新一代Conroe处理器测试的相继出炉,在感叹Conroe处理器性能强大的同时,发现其对内存延时却不是特别敏感,通过降低内存时序获得的性能提升是微乎其微。对此奇怪的现象,bit-tech.net做了一份更详细的Conroe处理器&内存测试报告,在此之前,首先让我们对Conroe处理器的核心架构有一个更深层的了解。

● 集成更大的二级缓存容量

与AMD的独立二级缓存设计不同,Core微架构采用共享二级缓存设计,即两个核心共享4MB的二级缓存。采用共享缓存的好处是非常明显的,除了缓存容量容量利用率较佳,也可以减少缓存数据一致性对缓存性能所造成的负面影响。此外,因共享L2缓存之故,两个核心的第一阶缓存可直接对传数据,毋需通过外部的FSB,进而改善性能。此外还有更为重要的一点,当其中一个核心空闲时,另一个核心可已使用全部4MB缓存,大大提高缓存的使用率,有效提高系统性能。

● 内建data prefetch(数据预先撷取器)

由Socket 939的Athlon 64开始,AMD便开始采用将内存控制器集成于CPU内核当中的设计,这种设计的好处在于,可以缩短CPU与内存之间的数据交换周期,以前都是采用内存控制器集成于北桥芯片组的设计,改成集成于CPU核心当中,这样一来CPU无需通过北桥,直接可以对内存进行访问操作,有效的提高了处理效率。但这样的设计存在的问题就是对内存延时要求很高,内存延时的提高会给系统性能带来很大的影响。

相对于AMD的处理器内部集成内存控制器,Intel平台的内存控制器设计在北桥芯片当中,这无疑为处理器访问内存带来更高的延时。不过Intel为了降低这种设计缺陷带来的影响,在Core微架构每个核心分别内建一组指令及二组数据预先撷取器,而共享的L2缓存控制器内建两组、可动态分配至不同的核心的数据预先撷取器,可根据应用程序数据的行为,进行指令与数据的预先撷取动作,让所需要的内存地址数据,尽量存放在缓存之中,减少存取内存的次数,这样的设计有效地提高了系统性能。

● 小结:

通过以上的资料显示来看,Conroe处理器内部集成更大的二级缓存容量以及内建data prefetch(数据预先撷取器)将是直接影响内存延时的重要因素,下面我们将通过测试来进一步验证。CPU选用了Core 2 Duo E6600与Core 2 Duo E6400,通过L2缓存容量的不同将更直观的对比内存延时带来的性能差异。

内存方面选用了三款来自Corsair(海盗船)的产品,三款内存全部为DDR2-800规格,仅仅在默认SPD时序方面有所不同。

处理器:

Core 2 Duo E6600 - 2.40GHz, 1066MHz FSB, 4MB L2 cache;

Core 2 Duo E6400 - 2.13GHz, 1066MHz FSB, 2MB L2 cache

内存:

2×1GB Corsair XMS2-6400C3 running at DDR2-800 with 3.0-3-3-9 timings;

2×1GB Corsair XMS2-6400C4 running at DDR2-800 with 4.0-4-4-12 timings;

2×1GB Corsair XMS2-6400PRO running at DDR2-800 with 5.0-5-5-15 timings.

关注我们