以小搏大!ARM Cortex A7全新架构简析

泡泡网CPU频道11月1日 如何在保证较长续航时间的前提下实现更高的计算性能一直是困扰智能手机的难题,你可以设计出具有强大性能的处理器芯片,但是你却很难实现长时间续航,而如果你为了节能推出低功耗芯片,那么芯片的计算能力又不能满足应用的要求,在这种矛盾中,移动芯片场上的做法是将高性能计算芯片跟低功耗计算芯片联合。

ARM欲推出Cortex A7超低功耗核心

在这方面的一个代表就是Nvidia的下一代Tegra3 SoC(代号为Kal-EI),Nvidia透露新一代SoC芯片将具备5颗运算核心,其中四颗能够提供较强的性能,并能在系统里显示出来,而另外一颗则能在较低功耗下进行计算。当移动设备在待机情况下,低功耗核心开启,完成emaile接收、SMS/MMS以及Twitter后台更新等运算,这时候高性能核心是关闭的以实现节能,而当系统需要较强运算能力时,另外的四颗高性能核心被唤醒参与运算,而低功耗的A9核心则会进入休眠状态。

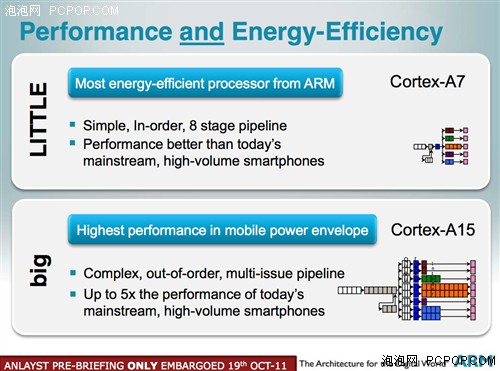

Nvidia的解决方案中,所有的芯片都是采用了相同或者相似的架构,而下面我们将要提到的不同架构核心的组合机制则差不多。目前ARM还不能提供足够低功耗的核心,因此Nvidia的解决方案里,低功耗的核心还是A9。而现在ARM正雄心勃勃得为Cortex家族增加这么一颗功耗足够低的运算核心、它既可以独立使用也可以作为一颗ISA协作核心跟高性能的A15核心联合使用。

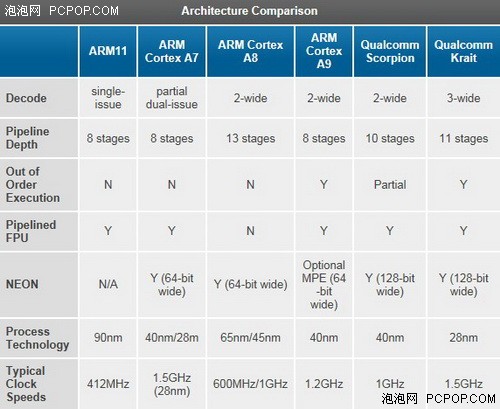

● 架构

其实自A9芯片开始,ARM就开始在乱序执行核心方面发力(在改进的并行计算中,指令的执行将根据任务进行重新排序),而在这方面Intel的X86是具有绝对优势的——从Pentium Pro时代Intel就开始推行这一运算机制。ARM将要推出的A15高性能核心即是继续延续A9的步伐,而A7则是走了相反的一条路——回归到Cortex A8的顺序执行,在并行计算中可以顺序执行两条指令,不过A7跟原来的A8还是有着很多不同的。

Cortex A7跟Cortex A15的区别

A8的设计可以追溯到2003年,后来ARM计划推出合成多核心的版本,用来提升频率和性能,不过受制于将新产品推向市场的时间和研发上的成本压力,“加强版”的A8核心计划夭折。如今得益于市场、制程等,ARM具有了卷土重来的资本,A7核心可以帮助ARM在未来几年内奠定在高频率、低功耗芯片方面的优势。

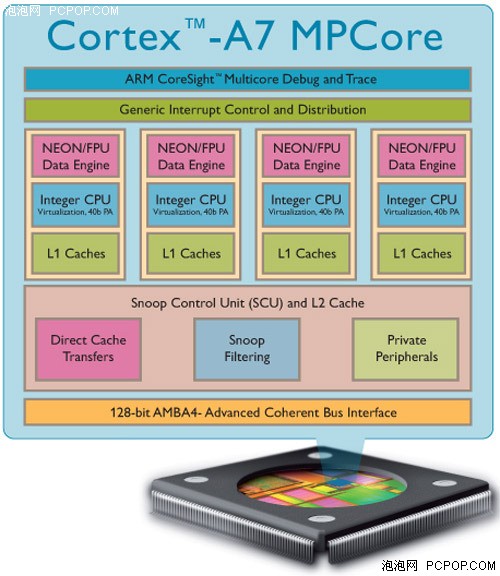

Cortex A7具备一颗8-stage的集成管线,并能支持双发。不过跟A8不同的是,A7不支持双发浮点或者说NEON指令集,不过有另外的指令集让A7实现单发。内部结构上的很多方面,A7都跟A8相似,不过在FPU等方面得到大幅加强。

限制带宽的设计让A7的芯片体积可以做到很小,ARM宣称28nm的单核Cortex A7的面积仅有0.5平方毫米,在工艺节点上,ARM希望合作厂商能将A7的die面积控制在A8的1/2甚至1/3,顺便一提,A9的die面积跟A8差不多,而高性能的A15则要比两者大得多,具体规格参见下表。

尽管限制了双发能力,ARM希望A7能提供比A8更强的每赫兹性能和整体性能,由于采用了相比A8更先进的预测器,A7的分支预测计算能力得到提升,更好的预测算法也使得这颗芯片更为节能,此外ARM还指出,它们在A7中采用了更低延迟的L2缓存(10 cycles),不过具体的情况还要取决于制造厂商。

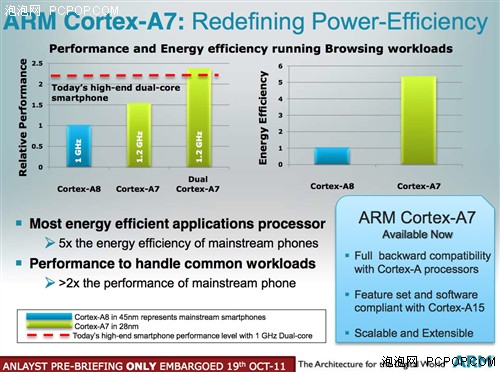

“Cortex A7重新定义了能效”

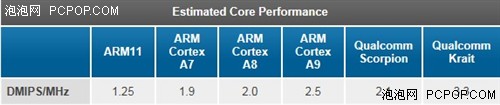

不过实际上,由于限制了双发带宽,Cortex A7的评估性能要比A8要低一些,具体的对比参见下表。

Cortex A7的评估性能不如A8(数值越大越好)

好消息是,Cortex A7能与Cortex A15实现100%的ISA兼容,而且A7能够支持新的虚拟化指令集、支持整数除法和40-bit内存寻址。也就是说任何运行在A15核心上的代码都可以在A7上运行,只是运算速度要慢一些。不过这一点让SoC芯片同时搭载Cortex A15和Cortex A7具有了实际意义,二者也可以根据任务负载的不同即时切换,ARM把这种机制称为“big.LITTLE”。

关注我们